无条件传送 查询式传送 中断方式传送 直接存储器存取 (DMA)

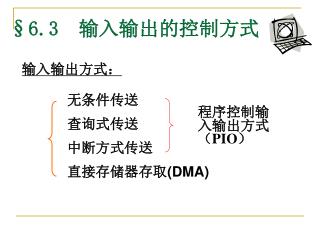

§6.3 输入输出的控制方式. 无条件传送 查询式传送 中断方式传送 直接存储器存取 (DMA). 输入输出方式:. 程序控制输入输出方式( PIO ). 一、无条件传送方式. CPU 不必查询外设当前的状态而无条件地进行数据的输入输出,数据交换与指令的执行是同步的,这种方式也称为同步传送方式。. 无条件传送流程. 适用于总是处于准备好状态的外设 优点:软件及接口硬件简单 缺点:只适用于简单外设,适应范围较窄. 实例:. +5V. 锁存器. 三态门. D1. Q. 1. D. 输出口地址 38F3H. CP.

无条件传送 查询式传送 中断方式传送 直接存储器存取 (DMA)

E N D

Presentation Transcript

§6.3 输入输出的控制方式 无条件传送 查询式传送 中断方式传送 直接存储器存取(DMA) 输入输出方式: 程序控制输入输出方式(PIO)

一、无条件传送方式 CPU不必查询外设当前的状态而无条件地进行数据的输入输出,数据交换与指令的执行是同步的,这种方式也称为同步传送方式。

适用于总是处于准备好状态的外设 • 优点:软件及接口硬件简单 • 缺点:只适用于简单外设,适应范围较窄

实例: +5V 锁存器 三态门 D1 Q 1 D 输出口地址38F3H CP D0 输入口地址38F0H

二、查询方式 CPU在数据传送前,必须先要查询一下外设的状态,若外设准备好才传送数据,否则要等待直到外设准备好为止 。

就绪信号(READY): 就绪:满,空、闲、不忙 • 输入 “就绪”说明输入接口已准备好送往CPU的数据,正等着CPU来读取;该状态也可用接口中数据缓冲器已“满”来描述。 • 输出 “就绪”说明输出接口已做好准备,等待接收CPU要输出的数据;该状态也可用接口数据缓冲器已“空”、或者用接口(外设)“闲”或 “不忙(Busy)”来描述。

多个外设查询传送流程 1号外设准备就绪? Y 对1号外设服务 N 2号外设准备就绪? Y 对2号外设服务 N … n号外设准备就绪? Y 对n号外设服务 N

对外设及接口的要求: • 外设应提供设备状态信息 • 接口应具备状态端口 特点: • 优点:软件比较简单 • 缺点:CPU效率低,数据传送的实时性差,速度慢 适用场合: • 外设并不总是准备好 • 对传送速率和效率要求不高

实例: • 外设状态端口地址为03FBH,第5位(bit5)为状态标志(=1忙,=0准备好) • 外设数据端口地址为03F8H,cpu往外设写数据的过程中,状态标志为1 ;外设接收完数据后状态标志为0。 • 试画出其电路图,并将DATA下100Byte的数据输出

74LS374 D7-D0 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 D7 D6 D5 D4 D3 D2 D1 D0 IOW ≥1 74LS138 & A9 | A3 3F8H G G2A G2B C B A CP Y0 外设 OE ≥1 A15 | A10 3FBH BUSY A2 A1 A0 Y3 ≥1 状态端口 74LS244 IOR 系统连接图: D7-D0 D5

程序: JZ AGAIN MOV AL,[SI] MOV DX,3F8H OUT DX,AL INC SI DEC CX JNZ AGAIN …… DATA DB 100 DUP (?) …… LEA SI, DATA MOV CX,100 AGAIN:MOV DX,3FBH IN AL,DX TEST AL,20H

三、中断方式 特点: • 外设在需要时向CPU提出请求,CPU再去为它服务。服务结束后或在外设不需要时,CPU可执行自己的程序 • 优点:CPU效率高,实时性好,速度快。 • 缺点:程序编制较为复杂。

前面三种传送方式的共同点: 均需CPU作为中介: • 软件: 外设与内存之间的数据传送是通过CPU执行 程序来完成的(PIO方式); • 硬件: I/O接口和存储器的读写控制信号、地址信号 都是由CPU发出的。 • 缺点:程序的执行速度限定了传送的最大速度(约 为几十KB/秒)

四、直接存储器存取方式 (Direct Memory Access,DMA) 特点: • 外设直接与存储器进行数据交换 ,CPU不再担当数据传输的中介者; • 总线由DMA控制器(DMAC)进行控制(CPU要放弃总线控制权),内存/外设的地址和读写控制信号均由DMAC提供。 • 可以达到很高的传输速率(几MB/秒)

DMA硬件结构图: MEM BUS … 控制信号 HOLD DRQ 外设 接口 DMAC CPU HLDA DACK

1、DMA控制器的功能 • 与CPU和外设接口的通信: • DRQ、HOLD、HLDA、DACK • 总线控制 寻址(修改地址计数器) 读/写命令 决定传送字节,判断是否结束 • 交换总线控制权 P261

2、DMA控制器的工作过程 (1)外设向DMAC发出DRQ信号; (2)DMAC收到请求后,向CPU发出HOLD信号; (3)CPU在完成当前总线周期后会立即发出HLDA 信号,对HOLD信号进行响应; (4)DMAC收到HLDA信号后,就开始控制总线,并向外设发出DMA响应信号DACK; (5) DMAC发出地址和相应的控制信号,实现外设与内存,或内存之间的直接数据传送; (6) 自动修改地址和字节计数器,判断是否结束。

CLK HLDA ALE A0-A9 有效地址 IOR MEMW IOW MEMR D7-D0 数据输入 DMA存储器写的时序: |S1 | S2 | S3 | Sw | S4 结束后撤销HOLD的同时,HLDA无效 无效

注意: • 传送前,CPU必须告诉DMAC传送部件,传送首地址,传送字节数; • 传送时,DMAC只负责送出地址及控制信号,数据并不经过DMAC。

2、DMA的传送方式 • 连续传送(块传送): DMAC在申请到总线后,将一块数据传送完后才释放总线,而不管DRQ是否有效。 • 单次传送(每次传送一个字节): 每个DMA周期只传送一个字节就立即释放总线。 • 按需传送(猝发传送): 只要I/O接口的数据缓冲可用,就可进行传送。此时I/O接口需要有一定大小的FIFO缓冲区。

允许DMA N DMA请求? Y DMAC请求总线 CPU响应, DMAC获总线控制权 DMA传送一个字节 地址增量,计数器减量 Y 块结束? N DMAC释放总线 数据块传送:

允许DMA 每次传送一个字节: DMA请求? N Y DMAC请求总线 CPU响应, DMAC获总线控制权 DMA传送一个数据 地址增量,计数器减量 Y 块结束? N DMAC释放总线 释放总线至少一个总线周期

按需传送: 允许DMA N DMA请求? Y DMAC请求总线 CPU响应, DMAC获总线控制权 DMA传送一个字节 地址增量,计数器减量 Y 块结束? N Y I/O的DRQ有效? N 释放总线,请求中断 无效,释放总线