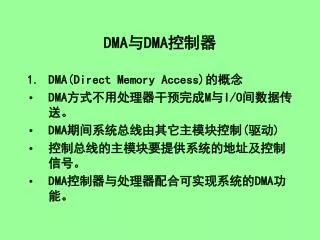

DMA

DMA. Control de E/S. E/S Programada (Polling) E/S por interrupciones DMA …. Transferencia de datos. MIENTRAS True Incrementar contador_datos SI contador_datos> total_datos ENTONCES SALIR FINSI Colocar dato en buffer destino Levantar señal de dato listo REPETIR

DMA

E N D

Presentation Transcript

Control de E/S • E/S Programada (Polling) • E/S por interrupciones • DMA …

Transferencia de datos MIENTRAS True Incrementar contador_datos SI contador_datos> total_datos ENTONCES SALIR FINSI Colocar dato en buffer destino Levantar señal de dato listo REPETIR ESPERAR HASTA QUE nuevo_dato_listo()? FINMIENTRAS

Computadora con DMA bus DMAC CPU Controlador LED LED Memoria Controlador Sensor Humedad Sensor Humedad

Computadora con DMA • DMAC y CPU comparten Bus de Memoria • Generalmente, E/S tienen mayor prioridad de acceso al bus • DMA crea ráfagas de tráfico en el bus

Protocolo DMA • El CPU configura el DMAC • El CPU arranca el DMAC y continúa con la próxima tarea • El DMAC realiza la transferencia de datos • Cuando finaliza la transferencia, el DMAC solicita interrupción al CPU • El CPU atiende la interrupción del DMAC

Computadora con DMA (2) • Computadora con más de un bus entre componentes • Bus de Memoria (CPU, DMAC, Memoria) • Bus de E/S (DMAC, Controladoras) • Posibilita paralelismo de transferencias de datos de dispositivos

Canal de E/S • DMA con mayor inteligencia (responsabilidad) del lado del DMAC • Se utilizan pequeños CPUs optimizados para E/S (IOPs) • Ejecutan instrucciones aritméticas y de saltos • El IOP negocia protocolos, envía comandos al dispositivo de E/S

Protocolo Canal E/S • El CPU coloca un programa de E/S en la memoria principal • El CPU indica la dirección de inicio del programa de E/S al IOP, y lo arranca • El IOP ejecuta el programa de E/S, cuando concluye el programa, emite interrupción al CPU • El CPU atiende la interrupción