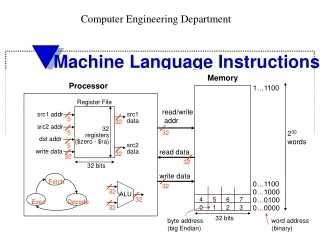

Machine Instructions

Machine Instructions. MACHINE INSTRUCTIONS. Machine Instructions – Hints and Tips. Hints and Tips. Machine Instructions – Hints and Tips 1.

Machine Instructions

E N D

Presentation Transcript

Machine Instructions MACHINE INSTRUCTIONS

Machine Instructions – Hints and Tips Hints and Tips

Machine Instructions – Hints and Tips 1 1 - STORE = FROM register TO storage2 - LOAD = FROM storage TO register3 - xxxxR = RR instruction, operands are both registers Example: AR,SR, LR, MR, DR, LTR4 - xxxxI = SI instruction, 1 operand is an immediate operand; it is the 2nd byte of the instruction, and is specified via an self-defining term (1 byte length) Example: MVI, SI, NI, OI, XI, etc5 - xxxxP = SS instruction, decimal packed operands, 2 lengths specification Example: AP, SP, MP, DP, ZAP6 - xxxxH = RX instruction, operands are 1 register and 1 halfword storage field Example: LH, SH, AH

Machine Instructions – Hints and Tips 2 7- Nxxxx = boolean instruction AND Example: NI, NC, N, NR 8 - Oxxxx = boolean instruction OR Example: OI, OC, O, OR 9 - Xxxxx = boolean instruction Exclusive OR Example: XI, XC, X, XR 10 - Most instructions (except CVD and the STORE ones STC, ST, STH, STCM, STM):symbol instruction receiver_operand,emitter_operand 11 - STORE and CVD instructions:symbol instruction emitter_operand,receiver_operand

Machine Instructions – Hints and Tips 3 12 - SS-L instructions (only one length) are: MVN, MVC, MVZ, NC, CLC, OC, XC, TR, TRT, ED, EDMK, MVCINMaximum length of each operand is 256 bytes.13 - SS-L1/L2 instructions (2 lengths) are: MVO, PACK, UNPK, ZAP, CP, AP, SP, MP, DPMaximum length for each operand is 16 bytes.14 – SRP instruction is an exception in the SS group: it has a reference to a length (1st half of the 2nd byte), and a round (in the other half of the 2nd byte)

Machine Instructions – Hints and Tips 4 15 – Use of Boolean instructions:OR = To force bits to 1 (turn ON bits)This can be used to (for instance) : (a) Set program flags to ON(b) Transform lowercase leters into uppercase letters (mask 0100 0000 : note in an EBCDIC table that the difference between lowercase and uppercase letters is always x’40’ (b’0100 0000’); turning the 2nd bit ON one can transform a lowercase letter into an uppercase letter. (c) Transform a binary number into the nearest high odd number (turning rightmost bit ON) Example: 1111 1110 is decimal 254. Turning rightmost bit ON: 1111 1111 it becomes decimal 255

Machine Instructions – Hints and Tips 4 15 – Use of Boolean instructions:AND = Force bits to 0 (turn bits OFF) This can be used to (for instance) : (a) Set program flags to OFF (b) Transform uppercase leters into lowercase letters (mask 1011 1111 : note in an EBCDIC table that the difference between uppercase and lowercase letters is always x’40’ (b’0100 0000’); turning the 2nd bit OFF one can transform an uppercase letter into a lowercase letter. (c) Transform a binary number into the nearest low even number (turning rightmost bit OFF) Example: 1111 1111 is decimal 255. Turning rightmost bit OFF: 1111 1110 it becomes decimal 254

Machine Instructions – Hints and Tips 4 15 – Use of Boolean instructions:XOR (ou exclusivo) = To invert bit setting (turns OFF if it is on, turns ON if it is OFF)This can be used to (for instance) : (a) Inverte program flags (toggle flags)(b) Transform lowercase into uppercase letter and vice-versa (mask 0100 0000) : letter x1xx xxxx becomes x0xx xxxx letter x0xx xxxx becomes x1xx xxxx(c) Transform binary even numbers into odd numbers and vice-versa: (mask 0000 0001) : rightmost bit is inverted(d) Exchange the contents of 2 area without a 3rd auxiliary area : XOR A,B + XOR B,A + XOR A,B(e) “Clear” (move binary zeros) an area : XOR A,A

Machine Instructions – Hints and Tips 4 16 – Arithmetic and bit shift operations (algebraic / logic operations):Unless othewise stated, these operations are done algebraically.This is always true for decimal packed fields.For binary fixed point numbers (in storage and/or registers) some operations that work algebraically and other operations work logically.Algebraic operations uses: 15-bit binary numbers + 1 bit sign for 2 byte numbers31-bit binary numbers + 1 bit sign for 4 byte numbers63-bit binary numbers + 1 bit sign for 8 byte numbersLogical operations assume numbers are always positive and uses: 16-bit binary numbers for 2 byte numbers 32-bit binary numbers for 4 byte numbers 64-bit binary numbers for 8 byte numbers

Machine Instructions Machine instructions (alphabetically)

Machine Instructions • (Some) Machine instructions (by group) • Storage to Storage move : MVC, MVZ, MVN, MVI, MVO, ZAP, MVCL, PACK, UNPK, MVCIN • - Register to Storage move : ST, STH, STM, STC, STCM, CVD • - Storage to Register move : L, LH, LM, IC, ICM, CVB • Register to Register move : LR, LPR, LNR, LCR, LTR • - Arithmetic with Storage fields in the packed format : AP, SP, MP, DP, SRP • - Arithmetic with Registers (fixed point binary) : AR, SR, MR, DR, ALR, SLR • Arithmetic with Register and Storage (fixed point binary) : A, S, M, D, AH, SH, MH, AL, SL • - Compare : CP, CLC, CLI, CLCL, C, CH, CL, CLM, CR, CLR • - Branch : BC, BCR • - Loop Control : BCT, BCTR, BXH, BXLE • - Edition : ED, EDMK • - Byte Translation and test: TR, TRT • - Register Shift : SLL, SRL, SLDL, SRDL, SLA, SRA, SLDA, SRDA • - Boolean Algebra : N, O, X, NR, OR, XR, NI, OI, XI, NC, OC, XC • - Load and branch : BALR, BAL, BAS, BASR, BASSM, BSM • - Misc : LA, TM, EX, SVC, MC, SPM, IPM, STCK, TS, CS, CDS

Machine Instructions Hints: what instruction do I have to use to move data from a place to another?

Machine Instruction Code 5A (RX Instruction) Condition code 00 Result = 0 01 Result < 0 10 Result > 0 11 Overflow Possible Interruptions 0005,0008 Machine Instructions - A A (ADD) Instruction A adds algebraically the binary number in the 1st operand and the bynary number in a storage field (2nd operand – a full-word). Result is loaded into 1st operand register. Examples: Suppose the operands with the length and values shown in the “before” line register 1st operand before 2nd operand before register 1st operand after 2nd operand after A 5,=F'259' 00.00.BF.D2 00.00.01.03 00.00.C0.D5 00.00.01.03 A 7,FULL 00.00.00.0D 00.00.01.03 00.00.01.10 00.00.01.03 A 7,4(2,8) 07.FF.FF.FE 00.00.00.01 07.FF.FF.FF 00.00.00.01 A 7,4(2) 07.FF.FF.FF FF.FF.FF.FF 07.FF.FF.FE FF.FF.FF.FF A 7,4(,8) 00.00.00.00 FF.FF.FF.FF FF.FF.FF.FF FF.FF.FF.FF Mach.Inst.Summary

Machine Instruction Code 4A (RX Instruction) Condition code 00 Result = 0 01 Result < 0 10 Result > 0 11 Overflow Possible Interruptions 0005,0008 Machine Instructions - AH AH (Add Halfword) This instruction adds algebraically two binary numbers. One of them is in the register specified as 1st operand, and the other is a storage half-word specified as 2nd operand. Before the operation is executed, the half-word is internally expanded to 32 bits by repeating (to the left) the leftmost bit (sign bit). Result is loaded into 1st operand register. Examples: Suppose the operands with the length and values shown in the “before” line register 1st operand before 2nd operand before register 1st operand after 2nd operand after AH 5,=H'259' 00.00.2B.C4 01.03 00.00.2C.C7 01.03 AH 5,HALF 00.00.00.0D 01.0D 00.00.01.1A 01.0D AH 5,4(2,8) 11.11.11.11 (decimal 286331153) 88.88 (decimal –30584) 11.10.99.99 (decimal 286300569) 88.88 AH 5,4(2) 11.11.11.11 (decimal 286331153) 78.88 (decimal +30856) 11.11.89.99 (decimal 286362009) 78.88 Mach.Inst.Summary

Machine Instruction Code 5E (RX Instruction) Condition code 00 Result = 0, sign not lost 01 Result <> 0, sign not lost 10 Result = 0, sign lost 11 Result <> 0, sign lost Possible Interruptions 0005 Machine Instructions - AL AL (Add Logical) This instruction adds logically two binary numbers. One of them is in the register specified as 1st operand, and the other is a storage full-word specified as 2nd operand. Both numbers are considered as positive 32-bit numbers. Result is loaded into 1st operand register. Examples: Suppose the operands with the length and values shown in the “before” line register 1st operand before 2nd operand before register 1st operand after 2nd operand after AL 5,=F'259' 00.00.00.00 00.00.01.03 00.00.01.03 00.00.01.03 AL 5,FULL 00.B0.C4.E2 00.00.00.01 00.B0.C4.E3 00.00.00.01 AL 5,4(2,8) 7F.FF.FF.FF 00.00.00.01 80.00.00.00 00.00.00.01 AL 5,4(2) FF.FF.FF.FF 00.00.00.01 00.00.00.00 00.00.00.01 AL 5,4(,8) 80.00.00.00 00.00.00.01 80.00.00.01 00.00.00.01 Mach.Inst.Summary

Machine Instruction Code 1E (RR Instruction) Condition code 00 Result = 0, sign not lost 01 Result <> 0, sign not lost 10 Result = 0, sign lost 11 Result <> 0, sign lost Possible Interruptions No interruptions occur Machine Instructions - ALR ALR (Add Logical Register) This instruction adds logically the contents of two binary numbers, both located in registers. Both numbers are considered as positive 32-bit numbers. Result is loaded into 1st operand register. Examples: Suppose the operands with the length and values shown in the “before” line register 1st operand before 2nd operand before register 1st operand after 2nd operand after ALR 7,12 00.B0.C4.E2 00.00.00.01 00.B0.C4.E3 00.00.00.01 ALR 8,8 7F.FF.FF.FF 00.00.00.01 80.00.00.00 00.00.00.01 ALR 10,10 FF.FF.FF.FF 00.00.00.01 00.00.00.00 00.00.00.01 ALR 10,10 80.00.00.00 80.00.00.00 00.00.00.00 80.00.00.00 Mach.Inst.Summary

Machine Instruction Code FA (SS Instruction – L1 e L2) Condition code 00 Result = 0 01 Result < 0 10 Result > 0 11 Overflow Possible Interruptions 0001,0004,0005,0007,000A Machine Instructions - AP AP (Add Packed) This instruction adds the contents of two packed numbers, both located in storage fields. Both numbers must be in the decimal packed format. Result is stored into 1st operand field. Examples: AP FLDA,FLDB before after FLDB 12.3C 12.3C FLDA 12.34.5C 12.46.8C AP FLDA,FLDA before after FLDA 45.2C 90.4C See more examples following: Mach.Inst.Summary

Machine Instruction Code FA (SS Instruction – L1 e L2) Condition code 00 Result = 0 01 Result < 0 10 Result > 0 11 Overflow Possible Interruptions 0001,0004,0005,0007,000A Machine Instructions - AP AP (Add Packed) Suppose the operands with the length and values shown in the “before” line 1st operand before 2nd operand before 1st operand after 2nd operand after AP HOWMANY,=P'1' 00.00.5F 1C 00.00.6C 1C AP ARL+2(5),ARL+7(2) 01.23.40.00.0C 98.7C 01.23.40.98.7C 98.7C AP TOTAL,2(3,7) 55.66.77.78.8C 11.11.1D 55.66.66.67.7C 11.11.1D AP 4(3,8),WALFA 01.99.9F 02.0C 02.01.9C 02.0C AP 7(07,8),14(2,3) 00.00.00.00.01.23.4C 00.5C 00.00.00.00.01.23.9C 00.5C AP GRANDTOT,SMALLTOT 00.00.00.0C 00.10.1C 00.00.10.1C Mach.Inst.Summary

Machine Instruction Code 1A (RR Instruction) Condition code 00 Result = 0 01 Result < 0 10 Result > 0 11 Overflow Possible Interruptions 0008 Machine Instructions - AR AR (Add Register) This instruction adds the contents of two binary numbers, both located in registers. The value of the register 2nd operand is added to the value of the register 1st operand. Result is stored into register 1st operand. Examples: Suppose the operands with the length and values shown in the “before” line register 1st operand before 2nd operand before register 1st operand after 2nd operand after AR 7,8 00.00.FF.FF 00.00.00.01 00.01.00.00 00.00.00.01 AR 2,2 00.00.FF.FF 00.00.FF.FF 00.01.FF.FE 00.01.FF.FE Mach.Inst.Summary

Machine Instruction Code 45 (RX Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions – BAL BAL (Branch And Link) BAL instruction is similar to the BALR instruction; the difference is that the address where the branch is to be made to (specified by the 2nd operand) is the instruction address in the base+displacement format (rather than the address in the register as in the BALR instruction). Note that to load the next instruction address (generally used as the return address when branching to execute a routine) BAL loads the last 4 bytes of PSW into 1st operand register. Examples: BAL loads the address of instruction labeled RETINS into register 9 BAL 9,ROUTINE BAL 14,WRTHDR BAL 7,2(5) BAL 7.2(,8) BAL 7,2(5,8) ... ... BAL 9,ROUTINE RETINS EQU * continuation ... ... ROUTINE ST 9,SAVEREG9 .... .... L 9,SAVEREG9 BR 9 Save register 9 (return address) into SAVEREG9 Restore return address Goback (to RETINS) Mach.Inst.Summary

Machine Instruction Code 05 (RR Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BALR BALR (Branch And Link Register) BALR instruction is similar to the BAL instruction; the difference is that the address where branch is to be made to (specified by the 2nd operand) is the value of the register 2nd operand (rather than the address in the base+displacement format as in the BAL instruction). Important: if the second operand is register zero, branch won’t be executed. Note that to load the next instruction address (generally the return address) BALR loads the last 4 bytes of PSW. Examples: BALR loads the address of instruction labeled RETINS into register 14 BALR 3,0 BALR 14,15 ... LA 15,ROUTINE BALR 14,15 RETINS EQU * continuation ... ... ROUTINE ST 14,SAVEREG .... .... L 14,SAVEREG BR 14 Save register 14 (return address) into SAVEREG LA loads the address of instruction labeled ROUTINE into register 15 Restore return address Goback (to RETINS) Mach.Inst.Summary

Machine Instruction Code 4D (RX Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BAS BAS (Branch And Save) • The address of the next instruction (following BAS) is loaded in the register 1st operand: • Bytes 5, 6 and 7 (last 3 bytes of PSW) are loaded into bytes 1, 2 and 3 of the register • Leftmost byte of register 1st operand is set to zero (this is the difference between BAS and BAL) • After loading the address, there’s a branch (jump) to the instruction specified in the 2nd operand. • Example: BAS 14,ROUTINE BAS loads the address of instruction labeled RETINS into register 9 bytes 1,2,3 and sets byte 0 with zero ... ... BAS 9,ROUTINE RETINS EQU * continuation ... ... ROUTINE ST 9,SAVEREG .... .... L 9,SAVEREG BR 9 Save register 9 (return address) into SAVEREG Restore return address Goback (to RETINS) Mach.Inst.Summary

Machine Instruction Code 0D (RR Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BASR BASR (Branch And Save Register) • The address of the next instruction (following BASR) is loaded in the register 1st operand: • Bytes 5, 6 and 7 (last 3 bytes of PSW) are loaded into bytes 1, 2 and 3 of the register • Leftmost byte of register 1st operand is set to zero (this is the difference between BASR and BALR) • After loading the address, there’s a branch (jump) to the instruction specified in the 2nd operand. • Example: BASR 14,15 BASR sets register 14 byte 0 with zero and loads the address of instruction labeled RETINS into bytes 1,2,3 of register 14 ... LA 15,ROUTINE BASR 14,15 RETINS EQU * continuation ... ... ROUTINE ST 14,SAVEREG .... .... L 14,SAVEREG BR 14 LA loads the address of instruction labeled ROUTINE into register 15 Restore return address Save register 14 (return address) into SAVEREG Goback (to RETINS) Mach.Inst.Summary

Machine Instruction Code 0C (RR Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BASSM BASSM (Branch And Save and Set Mode) • The address of the next instruction (following BASSM) is loaded in the register 1st operand: • Bytes 4, 5, 6 and 7 (last 4 bytes of PSW) are loaded into bytes 0, 1, 2, 3 of the register 1st operand • The value of register 2nd operand is loaded into bytes 4-7 of PSW; it includes leftmost bit (addressing mode) and (next) instruction address. • Due to this, the addressing mode is (re)set and a branch is provided. • Example: BASSM 14,15 • BASSM : • - Sets register 14 with the address of instruction labeled RETINS into register 14 (taken from PSW) • Loads contents of register 15 into PSW bytes 4-7 • (Addressing mode is set [from reg. 15 into PSW] ) and • (Branch to ROUTINE is executed) LA loads the address of instruction labeled ROUTINE into register 15 LA 15,ROUTINE ICM 15,8,AMODE BASSM 14,15 RETINS EQU * continuation ... ... ROUTINE ST 14,SAVEREG .... .... L 14,SAVEREG BR 14 ICM sets addressability mode into register 15 bits Restore return address Save register 14 (return address) into SAVEREG Goback (to RETINS) Mach.Inst.Summary

STATUS CODE 00 8 01 4 10 2 11 1 Machine Instructions - BC BC (Branch on Condition) There are 2 branch instructions: BC (RX Instruction) and BCR (RR Instruction). But they have many auxiliary mnemonic codes, named extended mnemonic codes. The branch instruction execution is based upon the status of Condition Code (remember? Those 2 bits of PSW) and the mask provided in the instruction (in the left half of its 2nd byte). The 4 different status Condition Code can be are: 00, 01, 10 and 11. For each one of them there is a corresponding code: The MASK occupies half byte and indicates the condition in which branch MUST be done. It can vary from X'0' to X'F' (decimal 0 up to 15). MASK 8, CC B'00‘ = Branch executed MASK 4, CC B'01‘ = Branch executed MASK 2, CC B'10“ = Branch executed MASK 1, CC B’11’ = Branch executed Mach.Inst.Summary

Machine Instructions - BC BC (Branch on Condition) One can do a combination of the masks, by adding their value. For instance, if mask is X'C', it means that branch must occur if Condition Code is in the 8 or 4 status (8 + 4 = 12). If mask is zero, no branch will be done (NOP/NOPR = no operation). If mask is 15 (X'F') branch will be done no matter waht is the Condition Code setting, because 15 = all codes added (8+4+2+1); it is an unconditional branch. Branch instructions with masks from 1 to 14 are conditional branches: the branch will only be done if Condition Code is apropriately set. See in the following slide the list of mnemonic codes, the valid masks and the extended mnemonic codes. Mach.Inst.Summary

Machine Instructions - BC BC (Branch on Condition) -------------------------------------------------------------------------- USE MNEMONIC MEANING BC/BCR EQUIVALENCE -------------------------------------------------------------------------- General B or BR Allways branches BC 15 or BCR 15 NOP or NOPR Never branches BC 0 or BCR 0 -------------------------------------------------------------------------- After BH or BHR Branch if A > B BC 2 or BCR 2 Compare BL or BLR Branch if A < B BC 4 or BCR 4 BE or BER Branch if A = B BC 8 or BCR 8 BNH or BNHR Branch if A < or = B BC 13 or BCR 13 BNL or BNLR Branch if A > or = B BC 11 or BCR 11 BNE or BNER Branch if A not = B BC 7 or BCR 7 -------------------------------------------------------------------------- After BO or BOR Branch if overflow BC 1 or BCR 1 Arithmetic BP or BPR Branch if R > 0 BC 2 or BCR 2 Instructions BM or BMR Branch if R < 0 BC 4 or BCR 4 BZ or BZR Branch if R = 0 BC 8 or BCR 8 BNP or BNPR Branch if R < or = 0 BC 13 or BCR 13 BNM or BNMR Branch if R > or = 0 BC 11 or BCR 11 BNZ or BNZR Branch if R not = 0 BC 7 or BCR 7 -------------------------------------------------------------------------- After TM BO or BOR Branch if all bits 1 BC 1 or BCR 1 BM or BMR Branch if mixed BC 4 or BCR 4 BZ or BZR Branch if all bits 0 BC 8 or BCR 8 BNO or BNOR Branch if some are 1 BC 14 or BCR 14 -------------------------------------------------------------------------- Notes: A = 1st operand ; B = 2nd operand ; R = 1st operand after compute Mach.Inst.Summary

Machine Instructions - BC BC (Branch on Condition) The extended menmonic codes are: B = Branch NOP = No Operation BH = Branch High BL = Branch Low BE = Branch Equal BNH = Branch Not High BNL = Branch Not Low BNE = Branch Not Equal BO = Branch If Overflow BP = Branch If Plus BM = Branch If Minus BZ = Branch If Zero BNP = Branch If Not Plus BNM = Branch If Not Minus BNZ = Branch If Not Zero BO = Branch If Ones BM = Branch If Mixed BZ = Branch If Zeros BNO = Branch If Not Ones Mach.Inst.Summary

BC (Branch on Condition) Machine Instruction Code 47 (RX Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BC BC (Branch on Condition) This instruction branches (or not) to another instruction. The format is: 1st byte = operation code = 47 2nd byte – 1st half = mask 2nd byte – 2nd half = index register for 2nd operand (branch instruction address) 3rd and 4th byte = 2 bytes with base+displacement of 2nd operand (branch instruction address) 1st operand is the mask; it indicates the condition branch must be done (or not). 2nd operand address is the address to branch to. If condition indicated by the mask is not satisfied, branch is not done, the execution resumes on the next intruction (instruction following BC). If condition indicated by the mask is satisfied, branch is done, the execution resumes on the intruction addressed by the 2nd operand. Mach.Inst.Summary

BC (Branch on Condition) Machine Instruction Code 47 (RX Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BC BC (Branch on Condition) If one uses the mnemonic code, only one “operand” must be specified: the address to branch to; in this case the mask is implicit in the mnemonic. Example: BC 8,AGAIN is the same as BE AGAIN BE is the same as BC 8. In this case, the branch will be done when condition code is 00. Other examples: B READ same as BC 15,READ BH AGAIN same as BC 2,AGAIN BL COMPARE same as BC 4,COMPARE BE 0(2) same as BC 8,0(2) BE 0(,4) same as BC 8,0(,4) BE 0(2,4) same as BC 8,0(2,4) NOP TOGGLE1 same as BC 0,TOGGLE1 Mach.Inst.Summary

BC (Branch on Condition) Machine Instruction Code 47 (RX Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BC BC (Branch on Condition) Other examples: B READ same as BC 15,READ BNH LOOP1 same as BC 13,AGAIN BNL LOOP2 same as BC 11,COMPARE BNE 0(2) same as BC 7,0(2) BZ 0(,4) same as BC 8,0(,4) BNZ 0(2,4) same as BC 7,0(2,4) BM BTAB(15) same as BC 4,BTAB(15) Mach.Inst.Summary

BCR (Branch on Condition Register) Machine Instruction Code 07 (RX Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BCR BCR (Branch on Condition Register) BCR instruction is similar to BC instruction. SEE BC INSTRUCTION. The format is: 1st byte = operation code = x’07’ 2nd byte – 1st half = mask (1st operand) 2nd byte – 2nd half = register 2nd operand containing the branch instruction address 1st operand is the mask; it indicates the condition branch must be done (or not). 2nd operand register must contain the address to branch to. If condition indicated by the mask is not satisfied, branch is not done, the execution resumes on the next intruction (instruction following BCR). If condition indicated by the mask is satisfied, branch is done, the execution resumes on the intruction addressed by the 2nd operand. If one uses the mnemonic code, only the register 2nd operand must be specified. See examples following: Mach.Inst.Summary

BCR (Branch on Condition Register) Machine Instruction Code 07 (RX Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BCR BCR (Branch on Condition Register) BCR 8,15 is the same as BER 15 BER is the same as BCR 8. In this case, the branch will be done when condition code is 00. Other examples: BCR 2,10 same as BHR 10 BR 7 same as BCR 15,R7 BNER 10 same as BCR 7,R10 BLR 15 same as BCR 4,R15 Mach.Inst.Summary

Machine Instruction Code 46 (RX Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BCT BCT (Branch on CounT) • This instruction has 2 operands: the first one is a register, and the second is an instruction address. • BCT subtracts 1 from the register 1st operand and after it compares the resulting number with zero. • · If result not equal to zero, it will provide a branch to the instruction referred in the 2nd operand • · If result is zero the branch won’t be done, processing will resume at the next instruction after BCT. • Examples: ... L 11,=F’200’ AGAIN CLC 0(3,5),CODE BE FOUND ... ... BCT 11,AGAIN NOTFND EQU * .... .... FOUND EQU * ... BCT 5,AGAIN BCT 2,0(4,7) BCT 2,0(4) BCT 2,0(,7) L loads into register 11 number of times loop must be repeated At the end of the set of loop instructions, BCT subtracts 1 from register 11. If zero not reached, branchs to AGAIN. If zero, resumes execution at NOTFND Mach.Inst.Summary

Machine Instruction Code 06 (RX Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BCTR BCTR (Branch on CounT Register) • BCTR instruction has 2 operands, both in registers. • BCTR subtracts 1 from the register 1st operand and after it compares the resulting number with zero. • · If result not = zero, a branch is provided to the instruction whose address is in the register 2nd operand • · If result is zero the branch won’t be done, processing will resume at the next instruction after BCTR. • IMPORTANT: If 2nd operand is register zero, branch won’t be done; this is often used just to • subtract 1 from a register, rather than, for instance, the S or SH instructions. Examples: LA 15,AGAIN L 11,=F’200’ AGAIN CLC 0(3,5),CODE BE FOUND ... ... BCTR 11,15 NOTFND EQU * .... .... FOUND EQU * ... BCTR 2,7 BCTR 4,0 L loads into register 11 number of times loop must be repeated LA loads into register 15 the address of AGAIN instruction At the end of the set of loop instructions, BCTR subtracts 1 from register 11. If zero not reached, branchs to AGAIN. If zero, resumes execution at NOTFND Mach.Inst.Summary

Machine Instruction Code 0B (RR Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BSM BSM (Branch and Set Mode) • The PSW’s addressing mode (bit 32) is loaded into bit 0 of the register 1st operand; bits 1-31 remain unchanged , and after that • PSW’s Bytes 4-7 is loaded with contents of register 2nd operand (including addressing mode bit and next instruction address) • Thus a addressing mode setting is done followed by a branch. • If 2nd operand is register zero, branch is not executed. • Example: • BSM 14,15 Mach.Inst.Summary

Machine Instruction Code 86 (RX Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BXH BXH (Branch on indeX High) 1st and 2nd operands are registers. 3rd operand is an instruction address. (a) The contents of register 2nd operand is added to the contents of register 1st operand, the result set into register 1st operand. (b) Result is compared with: · Contents of register 2nd operand (if it is an odd register) or · Contents of register following register 2nd operand (if it is an even register) If the compare result is ·Greater than it will be executed a branch to the instruction addressed by 3rd operand ·Less than or equal to the branch will not be executed; processing resumes at the instruction following BXH Mach.Inst.Summary

Machine Instruction Code 86 (RX Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BXH BXH (Branch on indeX High) Examples: BXH 7,8,AGAIN R7 = R8 + R7; If R7 > R9 Branch to AGAIN; * If R7 <= R9 next instruction BXH 7,9,AGAIN R7 = R9 + R7; If R7 > R9 Branch to AGAIN; * If R7 <= R9 next instruction BXH 7,9,8(4) R7 = R9 + R7; If R7 > R9 Branch to instruction * whose address is [ (contents R4) + x’008’ ] * If R7 <= R9 next instruction Mach.Inst.Summary

Machine Instruction Code 86 (RX Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BXH BXH (Branch on indeX High) L R7,=A(TABADRS) L R8,=A(20) L R9,=A(TABADRS+(HOWMANY-1)*LENGTH) NEXTITEM pointed item vs desired one if found, process it and go to TABLSEEN if not, point to next item BXH R7,R8,NOTFOUND B NEXTITEM TABLSEEN ... Example: Use in a search loop: R7 = begins with table address; incremented by element table length via R8 R8 = Table element length R9 = Last element address NOTFOUND : all table read, desired item not found. BXH 7,8,NOTFOUND R7 = R8 + R7; * If R7 > R9 all table already read; end search * If R7 <= R9 table not exhausted; continue search Mach.Inst.Summary

Machine Instruction Code 87 (RS Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BXLE BXLE (Branch on indeX Less or Equal) BXLE is similar to BXH instruction; the difference is that the branch is done if the result of the compare is Less or Equal. 1st and 2nd operands are registers. 3rd operand is an instruction address. (a) The contents of register 2nd operand is added to the contents of register 1st operand, the result set into register 1st operand. (b) Result is compared with: · Contents of register 2nd operand (if it is an odd register) or · Contents of register following register 2nd operand (if it is an even register) If the compare result is ·Less or Equal to : it will be executed a branch to the instruction addressed by 3rd operand ·Greater than : the branch will not be executed; processing resumes at the instruction following BXLE Mach.Inst.Summary

Machine Instruction Code 87 (RS Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BXLE BXLE (Branch on indeX Less or Equal) Examples: BXLE 7,8,AGAIN R7 = R8 + R7; If R7 <= R9 Branch to AGAIN; * If R7 > R9 next instruction BXLE 7,9,AGAIN R7 = R9 + R7; If R7 <= R9 Branch to AGAIN; * If R7 > R9 next instruction BXLE 7,9,8(4) R7 = R9 + R7; If R7 <= R9 Branch to instruction * Whose address is [ (contents R4) + x’008’ ] * If R7 > R9 next instruction Mach.Inst.Summary

Machine Instruction Code 87 (RS Instruction) Condition code Remains unchanged Possible Interruptions No interruptions occur Machine Instructions - BXLE BXLE (Branch on indeX Less or Equal) L R7,=A(TABADRS) L R8,=A(20) L R9,=A(TABADRS+(HOWMANY-1)*LENGTH) NEXTITEM compare pointed item vs desired one if found, process it and go to TABLSEEN if not, point to next item BXLE R7,R8,NEXTITEM NOTFOUND ... TABLSEEN ... Example: Use in a search loop: R7 = begins with table address; incremented by element table length via R8 R8 = Table element length R9 = Last element address NOTFOUND : all table read, desired item not found BXLE 7,8,NOTFOUND R7 = R8 + R7; * If R7 <= R9 table not exhausted; continue search * If R7 > R9 all table already read; end search Mach.Inst.Summary

Machine Instruction Code 59 (RX Instruction) Condition code 00 1st operand = 2nd operand 01 1st operand < 2nd operand 10 1st operand > 2nd operand 11 Condition code is not set as 11 after C Possible Interruptions 0005 Machine Instructions - C C (Compare) C performs an algebraic compare between a binary number in a register (1st operand) and a binary number in a storage field (a full-word, the 2nd operand). Example: C 9,CPO C 8,=F'0' C 13,=A(TABLE+430) C 1,2(4) C 1,2(,4) C 1,2(7,4) Mach.Inst.Summary

Machine Instruction Code BB (RS Instruction) Condition code 00 1st operand equal to 2nd operand, 3rd operand moved to 2nd operand 01 1st operand not equal to 2nd operand, 2nd operand moved to 1st operand 10 Condition code is not set as 11 after CDS 11 Condition code is not set as 11 after CDS Possible Interruptions 0004,0005,0006 Machine Instructions - CDS CDS (Compare Double and Swap) 1st and 3rd operands are even registers. They are considered an indication of: 1st operand: double-word composed by R1 and R1+1 3rd operand: double-word composed by R3 and R3+1 2nd operand is an storage field (double-word). Contents of 1st operand (R1 and R1+1) is compared with the contents of the double-word 2nd operand. If they are equal, the contents of the 3rd operand (R3 and R3+1) is stored into the 2nd operand double-word. If they are not equal, the contents of the double-word 2nd operand is loaded into the 1st operand (R1 and R1+1). See the following examples: Mach.Inst.Summary

Machine Instruction Code BB (RS Instruction) Condition code 00 1st operand equal to 2nd operand, 3rd operand moved to 2nd operand 01 1st operand not equal to 2nd operand, 2nd operand moved to 1st operand 10 Condition code is not set as 11 after CDS 11 Condition code is not set as 11 after CDS Possible Interruptions 0004,0005,0006 Machine Instructions - CDS CDS (Compare Double and Swap) CDS 4,8,DW Before: R4/R5 00.CC.DD.EE.FF.FF.FF.FF R8/R9 7D.48.C0.00.00.00.00.02 DW 00.BF.C4.20.50.CC.A0.00 After: R4/R5 00.BF.C4.20.50.CC.A0.00 R8/R9 7D.48.C0.00.00.00.00.02 DW 00.BF.C4.20.50.CC.A0.00 CDS 4,8,DW Before: R4/R5 00.BF.C4.20.50.CC.A0.00 R8/R9 7D.48.C0.00.00.00.00.02 DW 00.BF.C4.20.50.CC.A0.00 After: R4/R5 00.BF.C4.20.50.CC.A0.00 R8/R9 7D.48.C0.00.00.00.00.02 DW 7D.48.C0.00.00.00.00.02 Mach.Inst.Summary

Machine Instruction Code 49 (RX Instruction) Condition code 00 1st operand = 2nd operand 01 1st operand < 2nd operand 10 1st operand > 2nd operand 11 Condition code is not set as 11 after CH Possible Interruptions 0005 Machine Instructions - CH CH (Compare Halfword) CH performs an algebraic compare between a binary number in a register (1st operand) and a binary number in a storage field (a half-word, the 2nd operand). To do that, the 2nd operand is expanded (internally in the CPU) to 4 bytes, by repeating (to the left) 16 times the leftmost bit of the half-word. Example: CH 9,FLD 1st operand = R9; 2nd operand = FLD field CH 8,=H'0' 1st operand = R8; 2nd operand = half-word with zeros CH 13,=Y(TAB+430) 1st operand = R13; 2nd operand = half-word with address of TAB+430 CH 1,2(4) 1st operand = R1; 2nd operand = storage half-word which * address = value of index register R4 +0[base register omitted] + x’2’ CH 1,2(,4) 1st operand = R1; 2nd operand = storage half-word which * address = value of base register R4 +0[index register omitted] + x’2’ CH 1,2(7,4) 1st operand = R1; 2nd operand = storage half-word which * address = value of base register R4 +R7[index register] + x’2’ Mach.Inst.Summary

Machine Instruction Code 55 (RX Instruction) Condition code 00 1st operand = 2nd operand 01 1st operand < 2nd operand 10 1st operand > 2nd operand 11 Condition code is not set as 11 after CL Possible Interruptions 0005 Machine Instructions - CL CL (Compare Logical) The CL instruction compares logically the contents of register 1st operand and the contents of a storage full-word (2nd operand). Logical compare is done left to right, one bit at a time; the first couple of unequal bits finish the operation.. Examples: CL 9,CPO 32 bits of register 9 compared with 32 bits of 4-byte CPO CL 8,=F'0' 32 bits of register 8 compared with 32-bit of 4-byte full-word with zero CL 1,2(4) 32 bits of register 1 compared with 4-byte storage field * ( 2nd operand address = contents of index reg. 4 + displacement X’2’ [base reg. omitted = zero = not considered] ) CL 1,2(,4) 32 bits of register 1 compared with 4-byte storage field * ( 2nd operand address = [ index reg. Omitted = zero = not considered] + displacement X’2’ + base reg.4 ) CL 1,2(7,4) 32 bits of register 1 compared with 4-byte field * ( 2nd operand address = contents of index reg. 7 + displacement X’2’ + contents of base reg. 4 ) Mach.Inst.Summary

Machine Instruction Code D5 (SS Instruction – L) Condition code 00 1st operand = 2nd operand 01 1st operand < 2nd operand 10 1st operand > 2nd operand 11 Condition code is not set as 11 after CLC Possible Interruptions 0005 Machine Instructions - CLC CLC (Compare Logical Character) This instruction compares logically (left to right, one bit at a time) two storage fields. The first not equal couple of bits finish the compare. Examples: CLC CPOA,CPOB Only one length used = length of CPOA (e.g. 100 bytes) CLC AE+78(2),=C'*1'2-byte (AE+78 and AE+79) storage field is compared with * 2-byte storage field referenced via literal (contents = X’5CF1’) CLC 4(2,7),2(9) 2 bytes field (address = base register 7 + displacement X’4’) * is compared with storage field ( address = base register 9 + displacement X’2’ ) CLC ID,2(7) n-byte storage field ID is compared with n-byte storage field * (address = base register 7 + displacement X’2’ ) CLC 194(5,11),AE+3 5-byte storage field (address = base register 11 + displacement X’C2’) * is compared with 5-byte storage field ( address = AE+3 ) Mach.Inst.Summary

Machine Instruction Code 0F (RR Instruction) Condition code 00 1st operand = 2nd operand or both operands have zero length. 01 1st operand < 2nd operand 10 1st operand > 2nd operand 11 Condition code is not set as 11 after CLCL Possible Interruptions 0005,0006 Machine Instructions- CLCL CLCL (Compare Logical Character Long) This instruction compares two storage fields, in a similar way the CLC does. Both 1st and 2nd operands must be even registers. They indicate (each one of them) a pair of even-odd registers. We’ll call them: 1st pair = R1st and R1st+1; 2nd pair = R2nd and R2nd+1 The 1st operand (receiver field) address must be in the last 3 bytes (righmost) of R1st. The 2nd operand (sender field) address must be in the last 3 bytes (righmost) of R2nd. The 1st operand length must be in the last 3 bytes (rightmost) of R1st+1. The 2nd operand length must be in the last 3 bytes (rightmost) of R2nd+1. The leftmost byte of R2nd+1 must have the padding character. The leftmost byte of R1st, the leftmost byte of R2nd and the leftmost byte of R1st+1 are not considered in the operation. Example: CLCL 2,8 R2=1st operand register (dubbed as R1st above); note that R1st+1 = register 3 R8=2nd operand register (dubbed as R2nd above); note that R2nd+1 = register 9 Mach.Inst.Summary

Machine Instruction Code 0F (RR Instruction) Condition code 00 1st operand = 2nd operand or both operands are zero length. 01 1st operand < 2nd operand 10 1st operand > 2nd operand 11 Condition code is not set as 11 after CLCL Possible Interruptions 0005,0006 Machine Instructions- CLCL CLCL (Compare Logical Character Long) Compare is done one bit at a time, from left to right. When not 2 bits unequal are found OR when length of greater operand is exhausted compare is finished. If the operands have no equal kengths, the smaller one is extended with the padding character (internally, without any change in the field). If compare is finished due to 2 bits unequal encountered: - From the value in the rightmost 3 bytes of R1st+1 and R2nd+1 is subtracted the amount of equal bytes; if the difference was found with the padding character the rightmost 3 bytes of R1st OR R2nd+1 are zeroed (the ones who have the smallest length). - To the value of the rightmost 3 bytes of R1st and R2nd is added the amount of equal bytes. If both operands are equal (including the padding character, if needed): - The 3 rightmost bytes of R1st+1 AND R2nd+1 are zeroed. - To the 3 rightmost bytes of R1st AND R2nd is added the amount of equal bytes. In both cases : the leftmost byte of R1 and the leftmost byte of R2 are zeroed, and the leftmost byte of R1st+1 and R2nd+1 remain unchanged. Mach.Inst.Summary