Design of the Processor Control Unit Design

230 likes | 427 Views

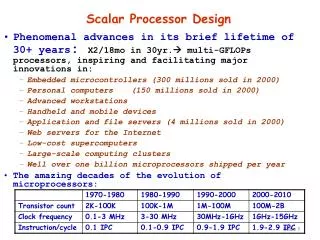

Design of the Processor Control Unit Design. ITCS 3181 Logic and Computer Systems 2014 B. Wilkinson Slides7.ppt Modification date: March 27, 2014. Control Unit Control unit needs to: Generate signals for each register transfer action and other operations specified, and

Design of the Processor Control Unit Design

E N D

Presentation Transcript

Design of the Processor Control Unit Design ITCS 3181 Logic and Computer Systems 2014 B. Wilkinson Slides7.ppt Modification date: March 27, 2014

Control Unit Control unit needs to: Generate signals for each register transfer action and other operations specified, and Be able to sequence through the steps for fetching/ executing the instructions in the program

Implementing Register Transfer Actions First consider P Q Pis the destination register and Q is the source register. There may be many sources and destinations. Convenient to attached all sources and destinations to a common set of wires:

Two logic signals required, one to select source, one to select destination: Transfer takes place when destination register activated with clock.

Timing Suppose need a sequence of steps to execute a particular instruction is: T0: S T T1: P Q T2: R P . . at times T0, T1, T2 ... , where S, P, and R are destinations and T, Q, and P are sources connected to the internal bus. Strictly, the action S T is done when T0 = 1

Example T5: MAR PC

Usually, other conditions needed apart for a timing signal being present. Example x.T5: MAR PC AND operation

Operations other than register transfer Sometimes, operations other than register transfer are specified. Example R P + R specifies an addition to be performed prior to the register transfer. Depending upon implementation, may need to be decomposed into a series of elementary steps. If we provide three separate buses, one for each source and one for the destination, possible to implement step in one time period - see next slide.

Processor with Three Internal Buses Control unit still has to provide necessary signals at correct times.

More complex steps - operation and data transfer Example Z X + Y

INSTRi . Tj: Z X + Y Similar logic circuits for each step.

Selecting source and destination registers - directly from instruction:

Fetch Cycle T0: MAR PC T1: MDR [MAR] (memory read operation) T2: IR MDR, PC PC + 4 This can could be done together given sufficient resources (data paths). Generally PC is a separate counter.

Implementing Execute Cycle Depends upon fetched instruction (in IR) Incorporating a signal to indicate particular instruction has been decoded, say INSTRi, in general we have: INSTRi.T3: S T INSTRi.T4: P Q INSTRi.T5: R P Execute cycle assumed to start at clock period T3. AND operation

General Arrangement for Execute Cycle Assumed to start at clock period T3:INSTRi.T3: S T INSTRi.T4: P Q INSTRi.T5: R P

More Specific Example Suppose op-codes are: Op-code I31I30I29I28I27I26 Arithmetic/logic: Register-register000aaa Register-constant 001aaa Load 010xxx Store 011xxx Branch 100ccc Jump: PC relative 101xxx Register indirect 110xxx Jump-and-Link 111xxx where: aaa specifies arithmetic/logic operation ccc specifies branch condition xxx are don’t cares Up to 7 operations allowed in this design (00…00 = no-op)