Pipelining FAQ

140 likes | 334 Views

Pipelining FAQ. Alex Jay CS 147 F’07. 1. What is pipelining?. Ans: Computer design technique to increase instruction throughput. Individual instructions are not sped up. Instead batches of instructions are more efficiently executed. 1. What is pipelining?.

Pipelining FAQ

E N D

Presentation Transcript

Pipelining FAQ Alex Jay CS 147 F’07

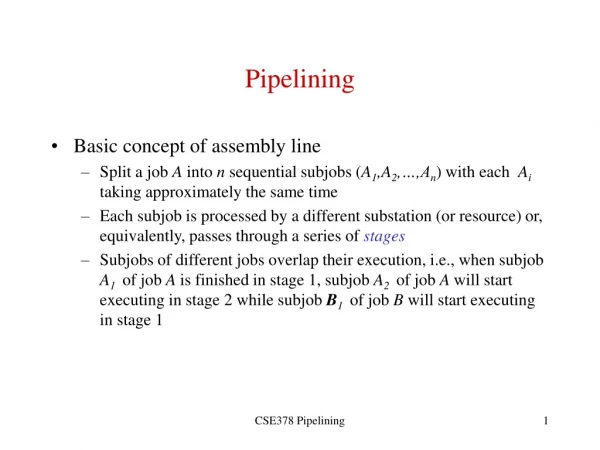

1. What is pipelining? • Ans: Computer design technique to increase instruction throughput. • Individual instructions are not sped up. Instead batches of instructions are more efficiently executed.

1. What is pipelining? • Execution time of pipelined and non-pipelined computer for a single instruction is the same. • When executing multiple instructions, pipelining decreases the speed of the entire job.

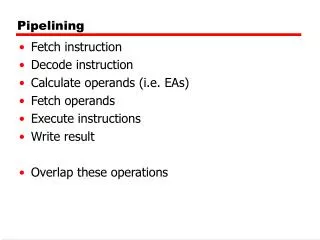

2. How does it work? • As each instruction moves through the pipeline stages, the next instruction is moved into the vacated pipeline stage • Ideally, each stage in a pipelined system takes an equal amount of time to complete.

2. How does it work? • 5 stage pipeline • IF = instruction fetch, ID = instruction decode, EX = execute, MEM = memory acces, WB = register write back

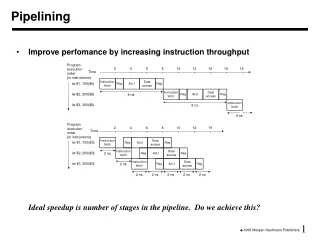

3. What are the performance gains? • Speedup: the ratio of the average non-pipelined instruction execution time per average pipelined execution time.

3. What are the performance gains? Instruction latency = 50+50+60+60+50+50= 320 nsTime to execute 100 instructions = 100*320 = 32000 ns

3. What are the performance gains? The length of pipelined stage = MAX(lengths of unpipelined stages) + overhead = 60 + 5 = 65 nsInstruction latency = 6x65 ns =390nsTime to execute 100 instructions = 65*6*1 + 65*1*99 = 390 + 6435 = 6825 ns

3. What are the performance gains? What is the speedup obtained from pipelining? Solution:Average instruction time not pipelined = 320 nsAverage instruction time pipelined = 65 nsSpeedup = 320 / 65 = 4.92

4. What are the disadvantages? • Non-pipelined design prevents branch delays. This makes them easier and cheaper to make. • Instruction latency is higher in pipelined designs because of added flip flops into the data path.

4. What are the disadvantages? Pipeline hazards. • Structural: The simultaneous use of the same resources. • Control: Program branches and overall flow. • Data: Data dependencies between instructions.

5. Solutions to hazards • Software inserted No-Ops into the instructions. • Hardware inserted Stalls. Similar to No-ops. • Branch prediction schemes. Assume a correct path and prefetch that instruction branch. ( can have up to 90% efficiency)