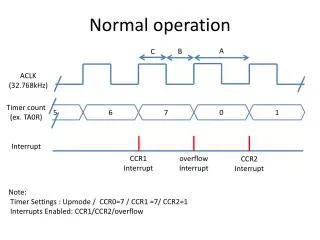

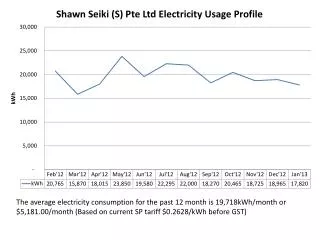

Normal operation

Normal operation. A. B. C. ACLK (32.768kHz). Timer count (ex. TA0R). 5. 6. 7. 0. 1. Interrupt. CCR1 Interrupt. overflow Interrupt. CCR2 Interrupt. Note: Timer Settings : Upmode / CCR0=7 / CCR1 =7/ CCR2=1 Interrupts Enabled: CCR1/CCR2/overflow.

Normal operation

E N D

Presentation Transcript

Normal operation A B C ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 0 1 Interrupt CCR1 Interrupt overflow Interrupt CCR2 Interrupt Note: Timer Settings : Upmode / CCR0=7 / CCR1 =7/ CCR2=1 Interrupts Enabled: CCR1/CCR2/overflow

Case A: Timer is cleared in A duration ex: TA0CTL |= (MC_1 | TACLR); Timer Clear Timer Restart ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 0 1 Interrupt CCR1 Interrupt overflow Interrupt CCR2 Interrupt In my understanding, this interrupt will happen. Is my understanding correct?

Case B: Timer is cleared in B duration ex: TA0CTL |= (MC_1 | TACLR); Timer Clear Timer Restart Will the value of TA0R not count up at this rising edge? ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 0 1 Is the value of TA0R clear when the TACLR was enabled Interrupt CCR1 Interrupt overflow Interrupt CCR2 Interrupt In my understanding, this interrupt will happen. Is my understanding correct?

Case C: Timer is cleared in C duration ex: TA0CTL |= (MC_1 | TACLR); Timer Clear Timer Restart Will the value of TA0R count up at this rising edge? ACLK (32.768kHz) Timer count (ex. TA0R) 0 5 6 7 1 2 Interrupt CCR1 Interrupt overflow Interrupt CCR2 Interrupt Is this interrupt occurred?