Overview

This overview discusses the need for a new design methodology for Globally Asynchronous, Locally Synchronous (GALS) systems and introduces an optimized integrated Quadrature Voltage-Controlled Oscillator (QVCO) for clock generation. The design strategy, simulations, and layout are presented, along with performance and power consumption considerations. The QVCO is designed using a prototype Gm-LC VCO with I-MOS varactors, achieving a tuning range of 10% and worst-case phase noise of -190 dBc/Hz. Future work includes incorporating the QVCO into a PLL design and completing other clock generator modules.

Overview

E N D

Presentation Transcript

An Optimized Integrated QVCO for Use in a Clock Generator for a NewGlobally Asynchronous, Locally Synchronous (GALS) Design Methodology.

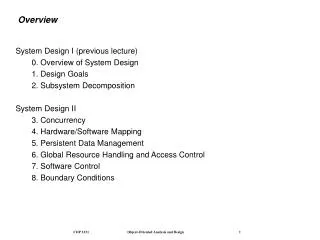

Overview • Background • Need for this new design methodology. • Why GALS? • What is novel in this design? • Need for QVCO • Design Strategy • Simulations & Layout • Conclusion

Multiplier cos wu sin wt CDA Phase Locked Loop Dual Sample & Hold Clock sin w(t-u) cos wt sin wu Multiplier Run SRFF1 SRFF2 Init1! Done! Init2! CLOCK GENERATOR Ref [1]

Simple Phase Locked Loop Source: http://www.uoguelph.ca/~antoon/gadgets/pll/pll.html

VCO Core Design Ref [4]

SIOS (Spiral Inductor On Silicon) Design Spiral Inductor Parameters Ref [6], [8]

Quadrature Generation Ref [12], [13]

Conclusion • A good compromise between area and overall power consumption was achieved. • A prototype quadrature –Gm LC-VCO for 650 MHz was designed in standard 0.25 µm, single-poly, five-metal, 2.5 V CMOS technology. • A tuning range of 10% was obtained through the use of I-MOS varactors.

Conclusion (Contd.) • SIOS achieving a Q of 5 were also created. • Simulated worst-case phase noise is -190 dBc/Hz at 600 MHz. • Occupies an area of 800 µm X 300 µm (0.24 mm2). • The designed VCO dissipates only 21 mW and operates from a single 2.5 V supply voltage.

Future Work • Incorporate QVCO into PLL Design. • Complete other Clock Generator Modules.

An Optimized Integrated QVCO for Use in a Clock Generator for a New Globally Asynchronous, Locally Synchronous (GALS) Design Methodology.