Mechanical Strain and Process strain Applied to Semiconductor Device 應用於半導體元件之機械應變及製程應變 研究生: 詹孫戎

450 likes | 903 Views

Mechanical Strain and Process strain Applied to Semiconductor Device 應用於半導體元件之機械應變及製程應變 研究生: 詹孫戎 指導教授: 劉致為 博士. Outline. Publication List Mechanically Strained-Si NMOSFETs PMOSFETs Mechanically Strained Si/SiGe HBTs Multi-Plane Reflector of RTP Wafer Bonding

Mechanical Strain and Process strain Applied to Semiconductor Device 應用於半導體元件之機械應變及製程應變 研究生: 詹孫戎

E N D

Presentation Transcript

Mechanical Strain and Process strain Applied to Semiconductor Device 應用於半導體元件之機械應變及製程應變 研究生: 詹孫戎 指導教授: 劉致為 博士

Outline • Publication List • Mechanically Strained-Si • NMOSFETs • PMOSFETs • Mechanically Strained Si/SiGe HBTs • Multi-Plane Reflector of RTP • Wafer Bonding • Process (Local) Strained-Silicon Simulation • Conclusions

Publication List • Mechanically strained strained-Si NMOSFETs • S. Maikap, C.-Y. Yu, S.-R. Jan, M. H. Lee, and C. W. Liu • EDL, VOL. 25, NO. 1, JANUARY 2004 • Mechanically strained Si/SiGe HBTs • F. Yuan, S.-R. Jan, S. Maikap, Y.-H. Liu, C.-S. Liang, and C. W. Liu • To be published in IEEE EDL, July, 2004 • Comprehensive study of mechanically strained strained-Si PMOSFETs • To be submitted to IEEE Trans. ED

Mechanically Strained-Si • Low cost • Package strain • Schematic diagram of the externally applied mechanical stress on the wafer • the channel is parallel to the azimuthal direction (Θ ) on the Y axis devices and the channel is parallel to the radial direction ( r ) on the X axis devices.

Bender design 底座立體圖02 底座立體圖01 墊片立體圖 上蓋立體圖

^ ^ ANSYS Simulation • (θ) strain lager than (r) strain • (r) strain degrades more

Mechanically Strained-Silicon NMOSFETs • Drain current vs. drain voltages for (a) control Si and strained-Si devices (WxL=25x25 m2) with and without mechanical strain.

^ ^ Mechanically Strained-Silicon NMOSFETs • Drain current enhancement with the distance from the centre of the wafer for the mechanically strained strained-Si and control Si devices.

Mechanically Strained-Si PMOSFETs • Drain current vs. drain voltage characteristics of (a) a control Si and (b) a strained-Si PMOSFET devices (WxL=25x0.6 m2) with and without mechanical strain of ~0.087%. The compressive and tensile strains are perpendicular to the channel using the one-end-bending method.

Effective Mess of Hole • Effective mass (meff) vs. uni-axial and bi-axial strain. Initially it is assumed that the heavy hole (mhh) = 0.54mo and light hole (mlh) = 0.5mo, where mo = 9.11x10-31 kg.

Mechanically Strained Si/SiGe HBTs • The Gummel plot of the SiGe HBT device without and with mechanical stress (strain ~0.028%). The base-collector bias is zero volts. (a) is the collector current and (b) is the base current. 13mm from the center (θ) strain ~0.033% ( r ) strain ~0.028% Average biaxial strain 0.028%

Experiment • The common emitter output characteristics with the constant base current. The SiGe HBT device with compressive mechanical stress has larger output IC than that without mechanical stress.

Multi-Plane Reflector of RTP • Arrangement of multi-plane reflector, lamp, and wafer. • High reflection on the side of reflector to compensate the radiation loss at the edge.

Multi-Plane Reflector Simulation • Increase the bonder temperature uniformity for 4 in full wafer bonding ψtot(x) ψdir(x) ψref(x) ψdir(x) is the irradiation intensity from the lamps. ψref(x) is the irradiation intensity from the reflector. ψtot(x) is total irradiation intensity [ =ψdir(x) + ψref(x) ]

Factors reflector length ll2 h w h_low_reflector h_high_reflector Unit (mm) 180 60 40 20 6 8 Multi-Plane Reflector design • factors in simulation

Wafer Bonding Process (a) Wafer alignment. (c) Apply pressure. (b) Set pressure device. (d) Remove spacer. • To have one initial contact and have only one bonding wave • Bonding on full wafer without defects are possible

IR-Viwer • IR-viewer • Home made: 0.2 M NT • Commercial: 1M NT IR-Viwer IR-bulb

Experiment • SOI, GOI applications Defects due to clean room particle

Experiment • No defect on 4” wafers

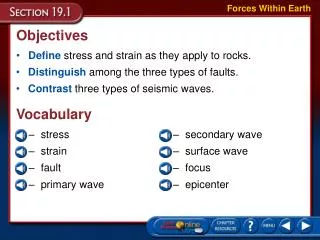

Process (Local) Strained-Silicon Simulation • Introduction • Why use strained-Si • because of physical size shrinking limitation • Need higher mobility μ • Strained-Si • Substrate (global) strained-Si • Process (Local) strained-Si

Substrate (global) strained-Si • Due to different lattice constant • Ge (SiGe) > Si • Effect • Tensile strain • Biaxial

Direction of Strain Change CMOS Performance Impact NMOS PMOS X Improve Degrade Y Improve Improve Z Degrade Improve Process (Local) strained-Si • Strain effect Schematic view of 3D process-induced strain components. εx is strain in the x direction εy is strain in the y direction εz is strain in the z direction • Impact of 3D Strain Effects on CMOS Performance. • Strain change = Increased tensile or decreased compressive strain

Process (Local) strained-Si ( Intel’s prescot CPU) • Cap-Layer: Ni4Si3 cap • STI: shallow trench insulator • Source/Drain: silicide ; CoSi2 ; TiSi2 ; SiGe TSMC 2003 IEDM Intel 2003 IEDM Intel 2003 IEDM

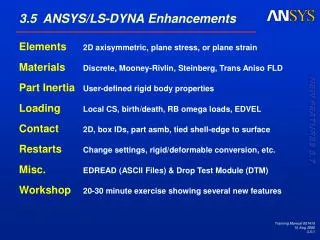

Simulation • Model • Thermal expansion ? MOS structure simulated by ANSY

ANSYS Simulation • stress is too small • εx≒0.04% • Process strain → 0.4% Enlarged figure of Fig. 5-2 . The origin of x axis is at the right edge of oxide.

Initial Stress • P-SiN: Plasma-CVD Silicon Nitride => compress stress • T-SiN: Thermal-CVD Silicon Nitride => tensile stress

ISE Simulation • Model • .25μm MOS • Initial stress: 1G • MOS structure simulated by ISE. • Channel length = 0.25 μm. Intel 2003 IEDM

Nitride Thickness • Thickness ↗ =>stress ↗ • not achieve our expectation The result of ISE simulation. The effect of the nitride thickness on the strain.

Nitride Thickness • 250nm→0.1% 70nm→0.038% • The result of ISE simulation. • The effect of the nitride thickness on the strain in the middle of channel.

Spacer • Intel spacer : sandwich Enlarged figure of Fig. 5-5. The nitride spacer no sandwich structure. Channel length = 0.25 μm. Spacer with sandwich structure. Channel length = 0.25 μm.

Spacer • Lager stress • Sandwich:0.046% • Control:0.038% The result of ISE simulation. The effect of the sandwich spacer structure on the strain. s channel : the stress of sandwich spacer in the channel. s nitride : the stress of sandwich spacer in the nitride cap. c channel : the stress of control spacer in the channel. c nitride : the stress of control spacer in the nitride cap.

shrink • .25μm → 50nm • Larger stress • 50nm • ε≒0.08% • 50nm sandwich • ε≒0.17% MOS structure simulated by ISE. Spacer with sandwich structure. Channel length = 50 nm.

shrink • Larger stress • 50nm • ε≒0.08% • 50nm sandwich • ε≒0.17% The result of ISE simulation. The effect of the shrinking dimension on the strain.

Conclusions • Mechanically Strained-Si • Multi-Plane Reflector designed and experiment • Wafer Bonding : No defect on 4” wafers • Process (Local) strained-Si • Initial stress • P-SiN: Plasma-CVD Silicon Nitride => compress stress • T-SiN: Thermal-CVD Silicon Nitride => tensile stress • Nitride thickness ; sandwich spacer ; size shrink • Result lager stress