CBM DAQ and Event Selection

340 likes | 536 Views

CBM DAQ and Event Selection. Walter F.J. Müller , GSI, Darmstadt for the CBM Collaboration International Workshop on Transition Radiation Detectors – Present and Future Cheile Gradistei, Romania, September 24-28, 2005. Outline. CBM (very briefly) observables setup FEE/DAQ/Event Selection

CBM DAQ and Event Selection

E N D

Presentation Transcript

CBM DAQ and Event Selection Walter F.J. Müller, GSI, Darmstadtfor the CBM Collaboration International Workshop onTransition Radiation Detectors – Present and FutureCheile Gradistei, Romania, September 24-28, 2005

Outline • CBM (very briefly) • observables • setup • FEE/DAQ/Event Selection • requirements • challenges • strategies TRD Workshop, Cheile Gradistei, September 24-28, 2005

CBM at FAIR ... evolving SIS 100 Tm SIS 300 Tm U: 35 AGeV p: 90 GeV Compressed Baryonic MatterExperiment TRD Workshop, Cheile Gradistei, September 24-28, 2005

CBM Physics Topics and Observables • In-medium modifications of hadrons onset of chiral symmetry restoration at high ρBmeasure: , , e+e- (μ+ μ-) open charm: D0, D± • Strangeness in matter enhanced strangeness productionmeasure: K, , , , • Indications for deconfinement at high ρB anomalous charmonium suppression ?measure: D0, D± J/ e+e- (μ+ μ-) • Critical point event-by-event fluctuations measure: π, K Good e/π separation Vertex detector Low cross sections→ High interaction rates→ Selective Triggers Hadron identification TRD Workshop, Cheile Gradistei, September 24-28, 2005

CBM Setup Radiation hard Silicon pixel/strip detectorsin a magnetic dipole field Electron detectors: RICH & TRD & ECAL: pion suppression up to 105 Hadron identification: RPC, RICH Measurement of photons, π0, η, and muons: ECAL TRD Workshop, Cheile Gradistei, September 24-28, 2005

CBM Setup... evolving μID ZCAL HBD Add ZCALto determine centrality Consider HPD for early lepton tagging (optional) Consider μID detector (optional) Consider various Silicon tracker implementations TRD Workshop, Cheile Gradistei, September 24-28, 2005

CBM Trigger Requirements assume archive rate: few GB/sec 20 kevents/sec • In-medium modifications of hadrons onset of chiral symmetry restoration at high ρBmeasure: , , e+e- open charm (D0, D±) • Strangeness in matter enhanced strangeness productionmeasure: K, , , , • Indications for deconfinement at high ρB anomalous charmonium suppression ?measure: D0, D±- J/ e+e • Critical point event-by-event fluctuations measure: π, K offline trigger trigger ondisplaced vertex offline drives FEE/DAQarchitecture trigger trigger trigger on high pte+ - e- pair offline TRD Workshop, Cheile Gradistei, September 24-28, 2005

Open Charm Detection • Example: D0 K-+ (3.9%; c = 124.4 m) • reconstruct tracks • find primary vertex • find displaced tracks • find secondary vertex target few 100 μm 5 cm • standard procedure.... • for CBM, this is in 1st level 'trigger' like for LHcB or BTeV (rip) first two planesof vertex detector TRD Workshop, Cheile Gradistei, September 24-28, 2005

CBM DAQ Requirements Profile • D and J/Ψ signal drives the rate capability requirements • D signal drives FEE and DAQ/Trigger requirements • Problem similar to B detection, like in LHCb or BTeV (rip) • Adopted approach: displaced vertex 'trigger' in first level, like in BTeV (rip) • Additional Problem: DC beam → interactions at random times → time stamps with ns precision needed → explicit event association needed • Current design for FEE and DAQ/Trigger: • Self-triggered FEE • Data-push architecture TRD Workshop, Cheile Gradistei, September 24-28, 2005

Buffer Conventional FEE-DAQ-Trigger Layout Especially instrumented detectors Detector L0 Trigger fbunch Trigger Primitives Dedicated connections FEE Cave Limited capacity Shack L1 Accept DAQ Modest bandwidth L2 Trigger L1 Trigger Limited L1 trigger latency Specialized trigger hardware Standard hardware Archive TRD Workshop, Cheile Gradistei, September 24-28, 2005

Limits of Conventional Architecture Decision time for first level trigger limited. typ. max. latency 4 μs for LHC Not suitable for complex global triggers like secondary vertex search Only especially instrumented detectors can contribute to first level trigger Limits future trigger development Large variety of very specific trigger hardware High development cost TRD Workshop, Cheile Gradistei, September 24-28, 2005

Buffer L2 Trigger L1 Trigger L2 Trigger The way out .. use Data Push Architecture Especially instrumented detectors Detector L0 Trigger fbunch fclock Trigger Primitives Dedicated connections FEE Timedistribution Cave Limited capacity Shack L1 Accept DAQ High bandwidth Modest bandwidth L1 Trigger Limited L1 trigger latency Specialized trigger hardware Standard hardware Special hardware Archive TRD Workshop, Cheile Gradistei, September 24-28, 2005

L1 Trigger L2 Trigger The way out ... use Data Push Architecture Detector fclock FEE Cave Shack DAQ High bandwidth Special hardware Archive TRD Workshop, Cheile Gradistei, September 24-28, 2005

L1 Select L2 Select The way out ... use Data Push Architecture Detector Self-triggered front-end Autonomous hit detection fclock FEE No dedicated trigger connectivity All detectors can contribute to L1 Cave Shack DAQ Large buffer depth available System is throughput-limited and not latency-limited High bandwidth Modular design: Few multi-purpose rather many special-purpose modules Special hardware Use term: Event Selection Archive TRD Workshop, Cheile Gradistei, September 24-28, 2005

Front-End for Data Push Architecture → power efficient front-end • Each channel detects autonomously all hits • An absolute time stamp, precise to a fraction of the sampling period, is associated with each hit • All hits are shipped to the next layer (usually concentrators) • Association of hits with events done later using time correlation • Typical Parameters: • with few 1% occupancy and 107 interaction rate: • some 100 kHz channel hit rate • few MByte/sec per channel • whole CBM detector: 1 Tbyte/sec → low jitterclock/time distribution → high bandwidth TRD Workshop, Cheile Gradistei, September 24-28, 2005

Typical Front-End Electronics Chain digital Filter Hit Finder Backend & Driver PreAmp Shaper ADC • Si Strip • Pad • GEM's • PMT • APD's Shaping time: 5-200 ns Sample rate: 10-100 MHz Dyn. range: 8...>12 bit 1/t Tail cancellation Baseline restorer Hit parameter estimators: Amplitude Time FIFO-Buffering Line protocol All in one mixed-signal chip TRD Workshop, Cheile Gradistei, September 24-28, 2005

Towards a Multi-Purpose FEE Chain digital Filter Hit Finder PreAmp Shaper ADC Several selectable input stages; →pos/neg signals → capacitance match switched capacitor filter → programmable shaping time programmable sampling rate programmable hit finder and estimator TRD Workshop, Cheile Gradistei, September 24-28, 2005

. . . Towards an Over All Architecture to/from next neighbor hit detection Hit Detector • Leading Edge • peak • … N Pre- Amplifier Blocks Programmable Finite State Machine DATA-out send Fast Readout DAC start Digital Pipeline Hit TDC TIMER stop Ain CLOCK we 1..N Event Buffers WE RE sample Digital Filters ADC different combinations • sampling rate • resoluion • power ANALOG FIFO Analog Filter leveraging TRAP knowledgeand expertise to/from next neighbor hit detection TRD Workshop, Cheile Gradistei, September 24-28, 2005

Atkin Fischer Brüning Deppe Muthers Tontisirin A CBM M-MPW Run • CBM organized a Multi-Multi Project Wafer run in UMC 0.18 μm CMOS • 6 different parts combined on a 5 x 5 mm2 wafer • submitted June to Europractice (IMEC) • dies (already cut) just delivered, now come the moments of truth Test structures Coordination: Marcus Dorn @ KIP PreAmp forSi Strip Content addressablememory DLL based TDC 12bit 50MSPS ADC Clock-Data recovery TRD Workshop, Cheile Gradistei, September 24-28, 2005

FEE Summary • Concrete R&D on FEE ASIC buildings blocks • MPWs done in 2005 covering essential blocks • analyze results, plan now next steps • Other ongoing developments: • Fast PreAmp-Shapers by H.K. Soltveit • in 0.35 μm AMS CMOS as spin-off of DETNI • in 0.13 μm IBM CMOS • next generation TAC by H. Flemming • FOPI and HADES work on RPC electronic • both learn to build mid-sized systems • self-triggered multi-hit TDC based on CERN HPTDC as HADES spin-off planned TRD Workshop, Cheile Gradistei, September 24-28, 2005

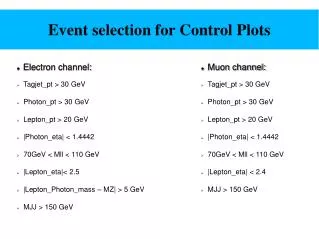

CBM DAQ and Online Event Selection • More than 50% of total data volume relevant for first level event selection • Aim for simplicity • Simple two layer approach: 1. event building 2. event processing neededfor D neededfor J/μ usefullfor J/μ STS, TRD, and ECAL data usedin first level event selection TRD Workshop, Cheile Gradistei, September 24-28, 2005

Logical Data Flow Concentrators:multiplex channelsto high-speed links Time distribution Buffers Build Network Processing resources forfirst level event selectionstructured in small farms Connection to'high level' selection processing TRD Workshop, Cheile Gradistei, September 24-28, 2005

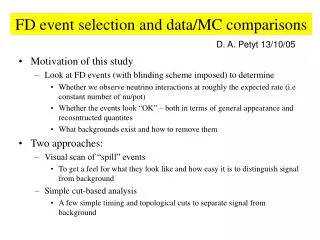

Bandwidth Requirements Data flow: ~ 1 TB/sec Gilder helps Moore helps 1st level selection: 10~14 operation/sec Data flow: few 10 GB/sec archive target: 1 GB/sec TRD Workshop, Cheile Gradistei, September 24-28, 2005

CBM DAQ / L1 Event Selection Requirements Profile Revisited • So far assumed: • D and J/Ψ measured simultaneously @ 107 int/sec • requirements driven by D (displaced vertex @ L1) • Current scenarios: • open charm runs with ~106 int/sec • look into D0, D±, Ds, and Λc • look into J/Ψ→ e+e- • look into J/Ψ → μ+μ- • look into p-A and p-p less computational B/W open charm L1 select Λc has cτ = 60μm only lower σ→ 107 int/sec all new game, still open even lower σ→ 108+ int/sec TRD Workshop, Cheile Gradistei, September 24-28, 2005

CBM DAQ / L1 Event Selection Requirements Profile Revisited MAPS/DEPFET pile-up again primary vertex determination ? events no longer well separated in time.... TRD Workshop, Cheile Gradistei, September 24-28, 2005

Feasibility & Options: BNet Data flow in Event Builder ~ 1 TB/sec TRD Workshop, Cheile Gradistei, September 24-28, 2005

Example: InfiniBand Switches • TODAY: • Voltaire ISR 9288 InfiniBand switch • 288 4x ports; non-blocking • cost today ~120 kEUR (or ~400 EUR/port) • 288 GByte/sec switching bandwidth • likely in a few years: • 288 4x port QDR • likely same or lower cost • 1152 GByte/sec switching speeds • adequate for CBM... • Conclusion: • BNet switch is not a major issue • There will be a COTS solution TRD Workshop, Cheile Gradistei, September 24-28, 2005

Feasibility & Options: PNet Initial proposal:Network of FPGA and CPU resources TRD Workshop, Cheile Gradistei, September 24-28, 2005

Shown in CBM Collaboration Meeting October 2004 Slide from CHEP'04 Dave McQueeneyIBM CTO US Federal TRD Workshop, Cheile Gradistei, September 24-28, 2005

The Cell Processor • one 'normal' PowerPC CPU (PPE) • 8 Synergistic Processing Element (SPE) each with • 256 kB memory; 128 x 128 bit register • 4 SP floating point units (SIMD) • designed for best GFlop/W • runs at ~ 3 GHz → 200 GFlop peak • Software support state: • Linux integration planned for 2.6.13 • SPE interface via spufs • gcc/gdb support for C/C++ • SIMD instructions via instrinsics... 221 mm2die sizein 90 nm Developed bySony, Toshiba and IBMMarket: VIDEOGAMESBudget: 500 M$ TRD Workshop, Cheile Gradistei, September 24-28, 2005

The Cell Processor cont. • Processors like the Cell offer • massive single precision floating point capabilities • large memory bandwidth • very good power efficiency (GFlop / W) • This is a very promising platform for L1 tracking • great for algorithms with a lot of arithmetic • probably much easier to handle than FPGAs • Next steps • analyze CA/KF tracker algorithm • determine the SIMD potential • re-implement it for speed • Note: might even improve time on a normal PC when SSE is used.... • and of course, get a Cell system ... • Note: 1000 Cell processors have 200 SP TFlop peak .... Even Intel has realizednow that this is theessential figure of merit TRD Workshop, Cheile Gradistei, September 24-28, 2005

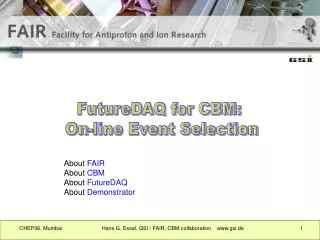

CBM FEE/DAQ Demonstrator • Mission: Provide a platform to • demonstrate essential architecture elements of the CBM FEE-DAQ concept • FEE: self-triggered, data push, conditional RoI based readout • CNet: combined data, time, control, and RoI traffic • TNet: low jitter clock and synchronization over serial links • BNet: high bandwidth, RDMA based architecture • E/DCS: integrated approach for DCS/ECS • provide test bed for all future FEE/DAQ prototyping in • hardware • firmware • controlware • software • perform beam tests with detector prototypes • form basis for medium-scale applications in intermediate-term experiments • Be operational by end 2006 • avoid cathedrals, go for the bazaar, try and learn • build a first generation (G1) demonstrator quickly TRD Workshop, Cheile Gradistei, September 24-28, 2005

DCB DCB DCB-TC OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE OASE MGT MGT MGT MGT MGT MGT GE GE GE GE GE GE OASE OASE OASE Mini Setup: Ethernet based FEE FEE FEE FEE FEE FEE FEE FEE Next to minimal test bench setupfew DCBclock/trigger from DCB-TCmodest data date via GE GE Switch PC PC GE GE TRD Workshop, Cheile Gradistei, September 24-28, 2005

The End Thanks for your attention We acknowledge the support of the European Community-Research Infrastructure Activity under the FP6 "Structuring the European Research Area" programme (HadronPhysics, contract number RII3-CT-2004-506078). TRD Workshop, Cheile Gradistei, September 24-28, 2005