EDA 原理及 VHDL 实现 (该课程为校级精品课程)

EDA 原理及 VHDL 实现 (该课程为校级精品课程). 何宾 2011.09. 课程内容. 第 1 章 数字系统 EDA 设计概论 第 2 章 可编程逻辑器件设计方法 第 3 章 VHDL 语言基础 第 4 章 数字逻辑单元设计 第 5 章 数字系统高级设计技术(*) 第 6 章 基于 HDL 设计输入 第 7 章 基于原理图设计输入 第 8 章 设计综合和行为仿真 第 9 章 设计实现和时序仿真. 课程内容. 第 10 章 设计下载和调试 第 11 章 数字时钟设计及实现(* ) 第 12 章 通用异步接收发送器设计及实现 (*)

EDA 原理及 VHDL 实现 (该课程为校级精品课程)

E N D

Presentation Transcript

EDA原理及VHDL实现(该课程为校级精品课程) 何宾 2011.09

课程内容 • 第1章 数字系统EDA设计概论 • 第2章 可编程逻辑器件设计方法 • 第3章 VHDL语言基础 • 第4章 数字逻辑单元设计 • 第5章 数字系统高级设计技术(*) • 第6章 基于HDL设计输入 • 第7章 基于原理图设计输入 • 第8章 设计综合和行为仿真 • 第9章 设计实现和时序仿真

课程内容 • 第10章 设计下载和调试 • 第11章 数字时钟设计及实现(*) • 第12章 通用异步接收发送器设计及实现(*) • 第13章 数字电压表设计及实现(*) • 第14章 软核处理器PicoBlaze原理及应用(*) • 注:带*的内容可根据课时的安排选讲

课程授课时间安排 • 该课程计划总学时:56 • 其中: • 理论教授课时:40 • 实验课时:16(大约安排实验6-7个)

课程教学用书 • 理论教学参考用书: • 1.何宾编著,<<EDA原理及VHDL实现>>,清华大学出版社。2011.09。 • 实验教学参考用书: • 1. 何宾编著,<<EDA原理及应用实验教程>>,清华大学出版社。2009.07 • 2. 何宾编著,<<数字与片上系统设计教程>>,清华大学出版社 • 课程网络资源: • http://bucteda.eefocus.com

课程所要解决的问题? • 回忆大二所学《数字电路》课程,还留在你们心 • 中的回忆: • 烦琐的卡诺图的化简(令你们和我一样抓狂) 如果让你手工化简多变量呢?估计你要崩溃 • 想想在做电子课程设计中,你们要花大量的时间和精力把区区几个74LSXX的门电路,用大量的导线连接在一起。这个过程估计你们谁也头疼。 你们也一定也知道在你们教科书的末尾好象提到 了一个称为硬件描述语言HDL的东西。老师没 讲,忽略了…,为什么啊?(这门课将要揭密)

课程所要解决的问题? • 当你们经历了以上的痛苦后,不知道你们想过下 • 面的问题没有? • 能不能让计算机帮助化简卡诺图?而且是多个 变量? • 能不能用一种芯片实现多个分离小规模数字IC的功能,并且在芯片内部将这些功能连接? • 设计数字系统能不能象C语言那样,只关心“如何描述”一个数字系统,而不是“如何具体实现”数字系统。

课程的重要性 • 该课程的学习对后续多门课程的学习起着重要的 • 作用,比如《微机原理》、《单片机》、《数字信 • 号处理 》、《通信原理》等和“数字”‘0’和‘1’有关课 • 程。 • 该课程是从事电子系统设计相关专业学生必须掌 • 握的内容。 • 大学生电子设计竞赛也把该课程内容作为参赛学 • 生应该掌握的内容之一。 • 你们慢慢体会吧…

数字系统EDA技术发展概述 • 电子设计自动化(Electronics Design Automation, • EDA)技术是一门迅速发展的新技术。 • EDA设计就是在计算机上通过特定功能的软件开 • 发工具,协助设计人员以全自动或半自动化方式完成 • 所要求电子系统的设计。

数字系统EDA技术发展概述 • EDA技术所涉及的领域相当广泛,业界一般将 • EDA技术分成: • 狭义EDA技术 • 广义EDA技术

数字系统EDA技术发展概述 • 狭义EDA技术,就是指以大规模可编程逻辑器件为 • 设计载体,以硬件描述语言为系统逻辑描述的主要表达方 • 式,以计算机、大规模可编程逻辑器件的开发软件及实验 • 开发系统为设计工具,通过有关的开发软件,自动完成用 • 软件方式设计的电子系统到硬件系统的: • 逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、 • 逻辑布局布线、逻辑仿真,直至对于特定目标芯片的适配 • 编译、逻辑映射、编程下载等工作 • 最终形成集成电子系统或专用集成芯片的一门新技 • 术,或称为IES/ASIC自动设计技术。

数字系统EDA技术发展概述 • 广义EDA技术,是通过计算机及其电子系统的辅助 • 分析和设计软件,完成电子系统某一部分的设计过 • 程。因此,广义EDA技术除了包含狭义的EDA技术 • 外,还包括: • 计算机辅助分析CAA技术(如PSPICE,EWB,MATLAB等), • 印刷电路板计算机辅助设计PCB-CAD技术(如PROTEL,ORCAD等) • 其它高频和射频设计和分析的工具等

数字系统设计技术发展历史 • 在过去的60年中,数字逻辑改变了整个世界, • 整个世界朝着数字化方向发展。今天我们所熟悉的 • 计算机在第二次世界大战后才出现在人类世界中。 • 表1.1给出了在计算机和数字逻辑发展历史上的 • 重大事件。 • 从该表可以看出数字逻辑设计技术经过了近400 • 年的逐步进化的过程。

摩尔定律-“统治半导体世界的法则” • 在1965年戈登.摩尔给出了世界上著名的“摩尔定 • 律”,并且于1975年进行了修正,在过去的35年以 • 来,被证明是非常正确的。 • 该定律的内容是:集成电路上可容纳的晶体管数 • 目,约每隔18个月便会增加一倍,性能也将提升一 • 倍,当价格不变时;或者说,每一美元所能买到的电 • 脑性能,将每隔18个月翻两倍以上。这一定律成为半 • 导体工艺不断发展的指南。

图1.1 摩尔定律与集成电路的发展趋势 摩尔定律-“统治半导体世界的法则”

数字系统设计技术发展历史 • 今天你们每个人都离不开一样东西-“电脑”,也就 • 是“微处理器”,但是以后在坐的各位,你们会发现 • 你们也离不开另一样东西-“可编程逻辑器件”,我这 • 门课程所介绍的东西。 • 你们也一定很好奇,别着急,听我后面慢慢介 • 绍。

现代数字系统设计发展阶段 • 现在数字系统设计的发展是随着计算机的出 • 现、集成电路制造水平和电子系统设计方法的发展 • 而不断发展的,主要经历了: • 计算机辅助设计(CAD,Computer Assist Design) • 计算机辅助工程设计(CAE,Computer Assist Engineering) • 电子设计自动化(EDA,Electronic Design Automation) 这几个阶段的特点和标志是什么?

集成电路芯片的发展历史 • 集成电路的发展分为了四个主要的阶段: • 1)在上世纪六十年代早期出现了第一片集成电路, • 其集成的晶体管数量少于100个,该集成电路称为小规 • 模集成电路(Small-Scale Integrated Circuit, SSI)。 • 2)在上世纪六十年代后期出现了中规模集成电路 • (Medium-Scale Integrated Circuit, MSI),其集成的 • 晶体管数量达到几百个。 • 3)在上世纪70年代中期,出现了大规模集成电路 • (Large-Scale Integrated Circuit, LSI),其集成的晶 • 体管数量达到几千个。

集成电路芯片的发展历史 • 4)在上世纪80年代早期,出现了超大规模集成电路 • (Very-large-scale-integrated, VLSI),其集成的晶体管 • 的数量超过了100,000个。 • 到上世纪80年代后期,集成的晶体管数量超过了 • 1,000,000个。 • 到上世纪90年代,集成的晶体管数量超过了 • 10,000,000, • 而到了2004年,这一数量已经超过了100,000,000个。 • 现在这一数量突破1,000,000,000个。

可编程逻辑器件的发展历史 • 1.第1阶段 • 上世纪70年代,可编程器件只有简单的可编程只读 • 存储器(PROM)、紫外线可擦除只读存储器 • (EPROM)和电可擦只读存储器(EEPROM)3种, • 由于结构的限制,它们只能完成简单的数字逻辑功 • 能。

可编程逻辑器件的发展历史 • 2.第2阶段 • 上世纪80年代,出现了结构上稍微复杂的可编程 • 阵列逻辑(PAL)和通用阵列逻辑(GAL)器件, • 正式被称为PLD,能够完成各种逻辑运算功能。

可编程逻辑器件的发展历史 • 3.第3阶段 • 上世纪90年代,Xilinx和Altera分别推出了与标准门 • 阵列类似的FPGA和类似于PAL结构的扩展性CPLD。 • 4.第4阶段 • 本世纪初,在该阶段出现了SOPC技术,是PLD和 • ASIC技术融合的结果。可编程逻辑器件厂商也提供了 • SOPC解决方案。 • 典型的,Xilinx和Altera也推出了相应SOPC FPGA • 产品,制造工艺达到65nm/40nm/28nm工艺水平,系 • 统门数也超过百万门。

数字系统设计方法概论 • 传统的数字系统的设计方法是画出逻辑图,这个图 • 包含SSI的门和MSI的逻辑功能,然后人工通过真值表和 • 通过卡诺图进行化简,得到最小的表达式,然后在基于 • TTL的LSI芯片上实现数字逻辑的功能。

数字系统设计方法概论 • 然而从图1.1可以看出,到了上世纪80年代后期和90 • 年代早期,这种设计方法遭遇了阻力。为什么呢? • 问题就是如何能画一个原理图,这个原理图包含成千 • 上万个门。正如在新的设计中可编程逻辑设备取代TTL芯 • 片那样,需要一种新的设计方法来设计数字电路。 • 今天,计算机辅助设计工具(Computer-aided Tools, • CAD),也称为EDA工具在当今的数字电路设计中是必须 • 的。

数字系统设计方法概论 • 在过去数十年越来越清楚的表明,今天的数字系统 • 的设计人员是通过写软件来设计数字电路的。这是最 • 重要的例子,说明了从传统数字系统设计方法向现代 • 的基于EDA工具的设计方法的转变。

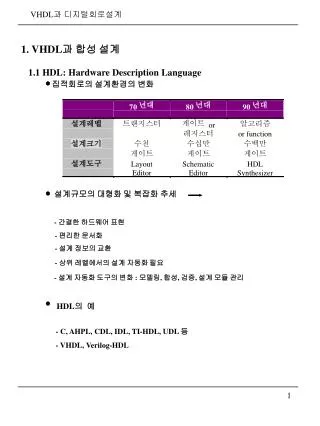

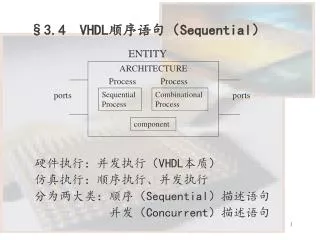

数字系统设计方法概论 • 今天的数字系统设计工程师使用硬件描述语言 • (Hardware Description Language, HDL)来设计数字系 • 统。 • 最广泛使用的HDL语言是VHDL和Verilog HDL。这 • 些语言允许设计人员通过写程序描述逻辑电路的行为来 • 设计数字系统。 • 程序能用来仿真电路的操作和在CPLD、FPGA或者专 • 用集成电路ASIC上综合出一个真正的实现。

SOP和POS表达式 • 术语“乘积”和“和”来自数学,用来描述与(AND) • 和或(OR)逻辑操作。 • “乘积”定义为多个变量之间的AND关系。 • “和”定义为任意数量逻辑变量的OR关系。 • 任何逻辑系统能用两种逻辑等效的方法表示,即积 • 之和(Sum of Product, SOP)形式和和之积(Product of • Sum, POS)形式。

SOP表达式 • 对于真值表的每一列,能生成一个乘积项,称为最 • 小项。 • 最小项通过对输入变量相关的值“相与”AND得到。 • 如果真值表特定的一行的变量值为1,则包含变量的名 • 字,比如x。如果真值表特定的一行的变量值为0,则 • 包含变量名字的取反,比如~x

SOP表达式 如果关心输出为‘1’的行, 可以发现当m1或者m2为真时, 输出z为真。因此,可以写z, 通过简单的OR上最小项(这些 最小项输出为1)。 输出z可以表示为: z=m1|m2=(~x&y) | (x&~y)

POS表达式 • 现在关注的不是真值表输出为1的行,而是关注的 • 是真值表输出为0的行。如图1.4所示。

POS表达式 • 注意在这种情况下z是非NOT最小项 m0和非最小 • 项m3,从前面的最小项的定义,使用德摩根De • Morgan定理,得到: • NOT m0=~m0=~(~x & ~y)=~~(x|y)=x|y • 称NOT m0为最大项M0。

POS表达式 得到z的POS表达式为: z=M0 & M3=(x | y) & ( ~x | ~y)

传统数字系统设计流程 • 传统的数字系统设计基于 • 传统的“人工”方式完成,当 • 设计目标给定后,给出设计 • 目标的真值表描述,然后使 • 用卡诺图对真值表进行化 • 简,得到最小的表达式,然 • 后使用TTL的LSI电路实现最 • 小的表达式,最后使用调试 • 工具和仪器,对系统进行调 • 试。

传统数字系统设计流程 • 下面将通过一个例子来说明这个 • 传统的设计过程。 • 1)设计目标:在一个共阳极的7段 • 数码管上显示相对应的0-F的值。 • 2)设计目标的真值表描述:图1.2 • 首先给出了七段数码管的符号表示,当 • 其是共阳极时,只有相应的段给低电平 • ‘0’时,该段亮,否则灭。

传统数字系统设计流程 • 3)使用卡诺图对真值表进行化简,图 • 1.3给出对于7段数码管e段的卡诺图化 • 简过程。 得到e段的最简单的逻辑表达式: • e=~x3& x0 | ~x3&x2&~x1 | ~x2&~x1&x0。 • 按照步骤3的过程分别得到a,b,c,d,f,g的最简逻辑表达 • 式,这些最简表达式使用积之和(Sum of Product, • SOP)和和之积(Product of Sum, POS)表示。

传统数字系统设计流程 • 4)使用相应的TTL门电路来实现各段的最小表 • 达式。 • 5)将这些门电路连接到7段数码管的各段,并 • 进行调试。

传统数字系统设计流程 • 从上面的流程可以看出,所有的过程都需要人工完 • 成,试想对于一个包含上百个逻辑门的多输入变量的结 • 构,根本无法使用人工化简卡诺图实现。同时后续的电 • 路调试和设计也需要很高的电路布局和布线的技巧,总 • 而言之,这样的设计对于复杂数字系统来讲效率太低 • 了。 • 我们需要进一步考虑的问题是,如何使用计算机帮 • 助设计者简化设计过程,自动地化简卡诺图,并且在芯 • 片内部自动实现布局布线。要实现这些要求,就必须使 • 用基于可编程逻辑器件的现代数字系统设计流程。

计算机最小化技术 • 从前面的数字系统设计流程中,可以看出使用卡诺 • 图很容易在不超过4个逻辑变量的布尔函数中找到最少数 • 目的乘积项。 • 然而许多的实际问题是,多于4个逻辑变量,并且卡 • 诺图并不能帮助进行逻辑表达式的化简。 • 计算机软件程序能够帮助对多于4个逻辑变量的布尔 • 函数进行简化。这些计算机方法使用基于表格的技术。 • 这些方法能自动的用机器进行计算。了解这些方法的工 • 作原理,将提供额外的智慧来简化布尔函数。 • 在本节所介绍的方法叫做“奎因-麦克斯基(Quine- • McCluskey)”方法。还有其它算法比这个算法的化简速 • 度更快,但是不能保证生成最优化的化简。

计算机最小化技术 --表格表示 • 以乘积和形式出现的乘积项,这个乘积项用于表示 • 布尔函数,称之为蕴含项。这是由于它暗示,如果任何 • 乘积项为1时,函数将为1。比如,对于这个函数: • f=x & ~y & z | ~x & ~z | ~x & y • 其中:x & ~y & z,~x & ~z和~x & y三个乘积项称为 • 蕴含项。在这种情况下,第一个乘积项是最小项m5。如 • 果最小项5用二进制数表示为101,这三个二进制数字分 • 别对应三个变量xyz(其中1对应的是变量的真值,0(~)对 • 应的是变量的假值)。这样101是x & ~y & z的另一种描述 • 方式。

计算机最小化技术 --表格表示 • 如果在一个乘积项中不包含一些变量时,插入一个 • 破折号“-”表示该变量,比如对于~x & ~z表示为0-0,~x • & y表示为01-。 • 因此称这这些为表格表示或者表格形式的乘积项。

计算机最小化技术 --表格表示 • 下面例子对图1.4的卡罗图用表格表示。该例子中在4 • 个圈起来输出为‘1’的每个乘积项使用了表格进行表示。 • 这样很容易对每个圈起来的集合的卡罗图符号得到表格 • 的表示。表格中最开始的两位是行标号,后两位是列标 • 号。如果圈起来的集合覆盖一个特殊位位置的‘0’和‘1’, • 该位位置变成‘-’。

计算机最小化技术 --表格表示 • 通过扩展卡诺图中所圈1的集合来产生乘积项是可 • 能的。比如,任意扩展它将覆盖图中的0,然后产生 • 乘积项或者蕴含项,叫做本源蕴含项。这样的本源蕴 • 含项中不能从乘积项中去除变量,并且暗含着逻辑功 • 能。下面将研究如何通过计算机找到这些本源蕴含项 • 的方法。