Active-VHDL Applications

Active-VHDL Applications. Presentation Outline. 1. Introduction 2. Design Entry Overview 3. Design Management Features 4. Simulation Input Methodologies 5. Using Stimulators 6. Waveform Viewer Features 7. VHDL Debugging Features 8. Vital Glitches and Delta Cycles

Active-VHDL Applications

E N D

Presentation Transcript

Presentation Outline 1. Introduction 2. Design Entry Overview 3. Design Management Features 4. Simulation Input Methodologies 5. Using Stimulators 6. Waveform Viewer Features 7. VHDL Debugging Features 8. Vital Glitches and Delta Cycles 9. VHDL Test Bench Overview

Presentation Outline (continued) 10. Creating and Executing Macro Commands 11. Visual BASIC Scripting Capabilities 12. VHDL Libraries Handling 13. Creating FPGA Design with Active VHDL 14. Using Active-VHDL with Foundation Software 15. Using FPGA Express with Active-VHDL 16. ACTIVE-VHDL Summary 17. Active-VHDL Resources

1.1 Why VHDL Simulation? “Why do I need a VHDL simulator if I can already simulate my VHDL macro using my current FPGA/CPLD vendor supplied netlist simulator?” Answer: FPGA/CPLD vendor supplied products only provide EDIF netlist based gate level simulation (i.e. Post-Synthesis) of your VHDL macro. If there is a problem in the functional description of your VHDL source, you have no way to trace/locate your error. You can only guess, or use a VHDL simulator to pinpoint your design problem.

1.2 Why VHDL Simulation? Below please find several reasons why VHDL simulation is becoming so important to the development and implementation of your FPGA/CPLD designs. • Large FPGA/CPLD devices- when developing large FPGA/CPLD devices VHDL provides a much easier and quicker way to enter and verify your design. Imagine placing 35,000 flip flops on a schematic. • Debugging- VHDL source code debugging takes you directly to the line of VHDL code that presents a conflict in the functionality of your design. There is no need to synthesize the code to perform a functional simulation. • Portability- using VHDL as a design description language allows for the reuse of VHDL code between projects independent of FPGA/CPLD vendor.

1.3 Why VHDL Simulation? • Flexibility- a project designed in VHDL can be easily customized to allow for VHDL based IP cores to be plugged in for system on a chip verification • Universal Language- VHDL has been adopted by every major FPGA/CPLD vendor as a standard language for entering high density designs. HDL design methodologies are the current trend in engineering technology. • Timing Simulation- most FPGA/CPLD vendors provide Vital support and SDF for back-annotation of timing delays from the fitter/place and route tool. These are two key elements to enable a VHDL simulator to provide timing simulation results. • Standard for the future- all new EDA tools are based on VHDL technology. Using VHDL standard is the best guarantee that the tools will be available 5-10 years from now (most schematics are obsolete in 2-3 years).

1.4 Aldec’s Answer to VHDL • PC based Win95/NT tool • Complete IEEE 1076-93 VHDL language simulator • New generation graphical user interface • Complete interactive source code debugger • Integrated graphical design entry tools • Links to ACTIVE-CAD and Xilinx Foundation schematics • Supports VITAL 95 simulation libraries • Test bench wizards: • Single process • WAVES based

2. Design Entry Overview • HDL Editor • HDL Wizard • Language Assistant • Finite State Machine Editor • Schematic can be imported from Active-CAD and Xilinx Foundation • Block Diagram Editor in Version 3.5 • Flexible User Interface Configuration

2.1 HDL Editor • Multi-file HDL editing, bookmarks, search • Color coding of HDL keywords • Integrated Syntax Check option • Controls VHDL debugging and cross-probing

2.2 Language Assistant • Language Assistant provides quick reference of VHDL structures • Templates are optimized for synthesis • Users can add their own templates

2.3 State Machine Editor • Graphical VHDL state diagrams editor • Supports Mealy and Moore diagrams • Generates VHDL code • Graphical simulation and debugging of state diagrams

2.4 State Machine Terms • States • Conditions • Transition • Transition priority • Reset transition • State actions • Transition actions • Default state • Trap State • State encoding

2.5 FSM Generated Code if CLK'event and CLK = '1' then if res = '1' then Test <= Add; q<="0000"; q<=q+1; else case Test is when Add => q<=q+1; if dir='1' then Test <= Sub; end if; when Sub => q<=q-1; if dir='0' then Test <= Add; end if; when others => null; end case; end if; end if;

3. Design Management Features • New Design Wizard • Design Explorer • Design Browser • Files Manager • Hierarchy Structure Navigation • Resource Files • Design Settings and Options • Design Archive/Restore

3.1 Design Wizard • GeneratesVHDL designskeleton • Creates symbolfor VHDL entity • SupportsHDL and state machine generation

3.2 Design Browser • Displays entire design hierarchy • Allows browsing the design structure • Locates any design objects, files, libraries • Invokes documents where objects are defined

4. Simulation Input Methodologies • Stimulators • Graphical Waveform Input • Test Bench Generation Wizard • User-defined Test Bench • WAVES simulation comparison • Simulation commands in files or console

Stimulator types: Value - 16#0F Formula - 1 0, 0 5 ns, -r 20 ns Hotkey - ‘R’ Clock - 10 MHz, 60 % d.c. Custom - from waveform Predefined - std. Clocks Forcing types: Override Deposit Drive 5. Using Stimulators

Adding/removing signals Applying stimulators Editing Waveforms Printing diagrams Copy/Paste to other programs Searching, bookmarks Expanding, defining buses Defining Radix Comments Measurements Multiple cursors Displaying glitches Analog display 6. Waveform Viewer Features

6.1 Waveform Viewer Window • Dynamic display of simulation results • User defined VHDL display types • Custom coloring and time measurements

Integrated Syntax Checking Code execution tracing Object value monitoring Event List Window Line Breakpoints Signal Breakpoints Watch Window Process state monitoring Variable editing FSM graphical debugging 7. VHDL Debugging Features

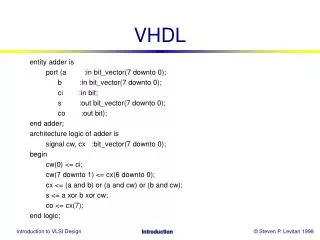

8. Delta Cycles signal X : std_logic := '0'; signal Y : std_logic; A: process begin wait for 100 ns; X <= not X; end; B: process (X) begin Y <= X after 10 ns; end;

8.1 Vital Glitches WARNING: VitalGlitch: GLITCH Detected on port O ; Preempted Future Value := 0 @ 261.714 ns; Newly Scheduled Value := 1 @ 261.749 ns;Time: 259049 ps, Iteration: 2, Instance: \UUT\Q_2_INT_FGBLOCK_LUTRAM_GLUT_OR2.

9. Why use VHDL Test Benches? • plays the role of a complete simulation environment for the analyzed system (unit under test) • contains both the UUT as well as stimulus generator for the simulation • response checker compares the actual UUT outputs with the expected values (e.g. WAVES based test bench) • very large and complex designs can only be fully tested using test benches; scripts and others methods are too cumbersome

9.1 VHDL Test Bench Overview • UUT - Unit Under Test • Stimulus Generator • transactions, min/max delays, fault conditions • Verifier • checking • reporting • comparison

9.4 Automatic Test Bench Generation • Test bench generation for selected architecture • IEEE WAVES standard support

9.5 Test Bench Wizard • Single process • converts waveforms to Test Bench • IEEE WAVES • golden vectors stored in *.VEC • compares functional and timingresults • user-defined comparison window • Standard IEEE 1029 library

10. Design Automation • Macro command execution • Implementation (synthesis, place & route tools) • VBA BASIC scripts execution

10.1 Creating and Executing Macro Commands • Automate simulation process • Batch mode verification • On-Line syntax reference • Compatible w/ ModelSimTM

11. Visual BASIC Scripting Capabilities • Visual BASIC engine and editor included • Create custom commands • Access to all tools functionality • Script debuggerincluded

12. VHDL Libraries Handling • Design Libraries • User-defined libraries • Standard libraries (IEEE) • FPGA vendor libraries • Source code included for some libraries • Library debugging available • Graphical Library Manager

12.1 Library Manager • Manage library files • List library contents

13. Creating FPGA Design with Active-VHDL • Multiple simulation configurations • Post Synthesis simulation (EDIF/VHDL) • Timing verification with SDF files • Synthesis scripts support • Implementation scripts • FPGA/CPLD libraries provided • Sample designs and interface guides for each vendor included

14. Using Active-VHDL with Foundation Software • Active-VHDL Link provided in F1.4 software • Any mixed VHDL/schematic design can be simulated • Schematics are automatically converted to VHDL • VHDL files can be modified within Active-VHDL • Routed VHDL netlist and SDF can be simulated • Built-in SIMPRIMS and UNISIM libraries • Support for LogiBLOX and LogiCORE models

14.1 Active-VHDL works with Active-CAD Synthesis NET2VHDL FITTER VITAL, SDF

16. ACTIVE-VHDL Summary • New generation VHDL design tools • All tools integrated in one environment • High performance simulation • Extensive VHDL debugging capabilities • For beginners and experts • Competitive prices

17. Active-VHDL Resources • Http://www.aldec.com/activevhdl • 30-days Evaluation • On-Line Documentation • EvitaTM Interactive Tutorial • Active-VHDL Series Books (1..4) • 1-800-487-8743 Hotline

Active-VHDL Lab 1 Training Guide

Lab 1 Outline 1. Creating a Behavioral Design 2. Creating CNT_BCD module 3. Simulating with the waveforms 4. Simple Debugging Features 5. Using Test Bench Wizard 6. Creating and debugging FSM 7. Creating top level in Active-CAD

1.1 Creating a behavioral design • The training is based on a simple frequency meter design with BCD counter and 7-segment LED display. • The method of measurement is to compare input signal frequency with a reference clock signal that is slower then measured signal. • To measure the input frequency you need to set START signal to 1 logical value and hold it, setting START back to 0 logical value finishes the measurement and resets the meter for the next measurement cycle. • The design contains 3 blocks described in behavioral VHDL code. • The design is then synthesized and implemented in XILINX FPGA.

1.2 Creating a behavioral design • The entire design is described by the following diagram:

1.3 Creating a behavioral design • The following blocks are used in the design: • HEX2LED - 7 segment display converter • CNT_BCD - 4 decades BCD counter • CONTROL - frequency meter control state machine

1.4 Creating a behavioral design • This section will show the following operations: • How to use New Design Wizard to create new design • How to use New Source File Wizard to create source files • How to create your own VHDL code • Basic operations in Design Browser • Basic operations with Language Assistant

1.5 Creating a behavioral design • On the File menu click New Design to invoke the New Design Wizard window • In the Type the design name field, enter FREQ_METER • Click on the Next button to advance to the next page

1.6 Creating a behavioral design • Select Create an empty design option • Click on the Next button to advance to the next page