State Machine Realizations

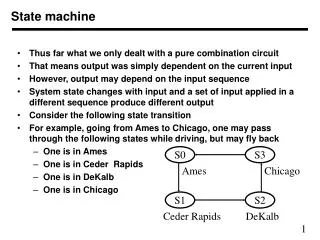

This lecture explores the concept of one-hot encoding within the context of state machines, particularly focusing on its application in designing a digital control circuit for a successive approximation A-to-D converter. One-hot encoding allows for efficient representation of states with minimal excitation equations, making it ideal for systems with a distinct set of outputs indicating the current state. The lecture also discusses bit-slice logic, where uniform logic is adapted across multiple slices for effective VLSI implementations. Gain insights into how to implement these concepts in digital design.

State Machine Realizations

E N D

Presentation Transcript

State Machine Realizations ECE 561 - Lecture 6

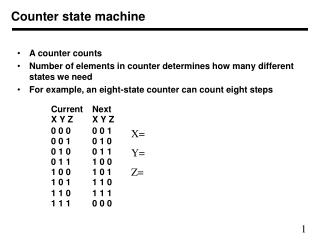

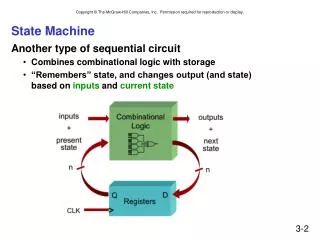

Another type of system • One Hot encoding – only one of the state flip-flops is ever a 1. All the other state flip-flops are a 0. • Requires n flip-flops for an n state machine. • Ideal for a state machine having a set of 1-out-of-s coded outputs indicating the current state ECE 561 - Lecture 6

A D-to-A Converter • Design a successive approximation A-to-D converter • Will do a 10 bit conversion • Another designer is responsible for the design of the analog comparator • A different designer is responsible for the D-to-A converter within the unit • Your job is to design the digital control circuitry ECE 561 - Lecture 6

The system • The D-to-A system ECE 561 - Lecture 6

The States • The states are fairly simple ECE 561 - Lecture 6

One Hot Encoding • There are 10 distinct state during conversion – each state represents which bit is being converted • Also an initial state and the conversion complete state • The architecture lends itself to one-hot encoding of the states ECE 561 - Lecture 6

Why One hot encoding • One hot encoding typically leads to minimal excitation equations • Minimal excitation equations = lower complexity logic • Lend itself to bit slice logic ECE 561 - Lecture 6

Bit slice logic • Bit slice logic – the same logic is used for each slice. There may be minor modifications needed for the end slice. • Excellent for VLSI implementations ECE 561 - Lecture 6

The slice here • Slice is simply repeated for the number of bits. ECE 561 - Lecture 6