SEU Hard Counters

SEU Hard Counters. Hamming codes TMR Johnson Ring Counters Ripple counters. Error Correction Methods. Hamming Codes Triple-Modular Redundancy Results could be applied to arbitrary state machines Assumptions: Error correction mechanism must operate in real time

SEU Hard Counters

E N D

Presentation Transcript

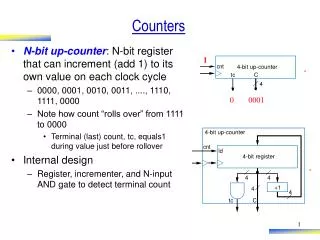

SEU Hard Counters Hamming codes TMR Johnson Ring Counters Ripple counters

Error Correction Methods • Hamming Codes • Triple-Modular Redundancy • Results could be applied to arbitrary state machines • Assumptions: • Error correction mechanism must operate in real time • Cannot stop, reset, or return counter to previous value to correct output

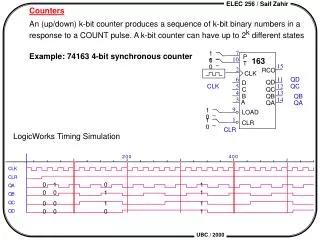

Hamming Codes • For any m≥2, there is a Hamming code with 2m-1 total bits and 2m-1-m information bits giving single error correction

4-bit Hamming Code Counter Next Count Logic NC3:0 Next Parity Logic NP2:0 Count Bit Register C3:0 Parity Bit Register P2:0 Correction Logic Cout3:0 Corrected count output Cout 3:0

Logic Equations • Correction Logic: • S0 = C2 C1 C0 P0 • S1 = C3 C2 C1 P1 • S2 = C3 C1 C0 P2 • E0 = S0 (S1) S2 • E1 = S0 S1 S2 • E2 = S0 S1 (S2) • E3 =(S0) S1 S2 • Corrected Output • Cout0 = C0 E0 • Cout1 = C1 E1 • Cout2 = C2 E2 • Cout3 = C3 E3 • Next Parity Logic: NP0 = NC2 NC1 NC0 NP1 = NC3 NC2 NC1 NP2 = NC3 NC1 NC0 • Next Count Logic: NC0 = Cout0 NC1 = NC1 Cout0 NC2 = NC2 (Cout1Cout0) NC3 = NC3 (Cout2Cout1Cout0)

Gate Count for 16-bit Hamming Counter Assuming 2-input gates

TMR Bit Structure Note that this structure has no capability to correct itself if a bit flips

4-Bit TMR Counter Next Count Logic NC3:0 4-Bit TMR Register Cout3:0 Corrected count output Cout3:0

Gate Count for 16-bit TMR Counter Assuming 2-input gates

Comparing 16-bit Hamming and TMR Counters • Strength of bit-flip immunity • Hamming: effects of bit flip must propagate through the correction logic before being corrected => the output might be wrong for some time period • TMR: bit flip has no effect on the voted output • TMR has stronger bit-flip immunity

Hamming vs. TMR • Device count 16-bit Hamming uses 161 devices 16-bit TMR uses 158 devices • About the same • But: Hamming uses 21 flip-flops TMR uses 48 flip-flops • TMR has much higher clock loading

Johnson Ring Counters • Advantage: glitch-free decoding • Disadvantage: low encoding efficiency

Cascading Ring Counters 2-bit cascadable ring counter stage Will count to 4 => 8 stages will count to 48 = 216 with 16 bits

16-bit Ring Counter • Assume each flip-flop is a TMR structure • 16-bit ring counter requires 8 stages • Device count: • High clock loading • High parts count • Glitch-free decoding, each stage only

Voting Ripple Counters Reference: SEU Induced Anomalous Behavior of Voted Ripple Clocks, 1999 MAPLD International Conference, R. Barto

Characteristics of Ripple Counters • Useful for producing low frequency clocks • Much lower parts count than fully synchronous counters • May only be reset on power-up • Voting at end of chain uses much fewer parts than does voting at every stage

Consequences of Voting at End of Chain • Bit flips in counter chains change the count • May be considered to induce phase shifts • Phase changes persist if the counter is not reset • Phase shifts induced over time are additive • Voting counters having undergone phase changes produces anomalous results

Phase Shifts in Counter Chains • Flip in MSB shifts counter 180º • In general, for an n-bit counter, the phase shift induced by a flip in bit i is 180º/2n-1-I • A flip in bit i can also be considered to add 2i to the value of the counter

Voting Phase-shifted Counters Voter output correct in spite of phase shifts

Anomalous Counter Output Phase shifts sufficient to cause voter output to be incorrect

Alternative Design Techniques • Voting at every counter stage instead of at end • Requires more space • Eliminates anomalous behavior • Periodically resetting the counters • Smaller hardware impact than voting every stage • Anomalous behavior still possible, but much less likely