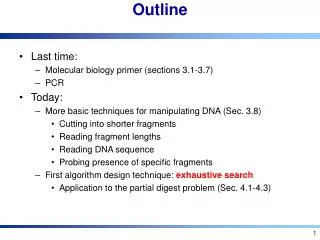

Outline

Outline. Computer Organization Computer architecture Central processing unit Instruction execution Devices Interrupts. Please pick up Homework #1 from the front desk if you have not got a copy. Review: System Overview. Pattern. Jacquard Loom. Variable Program. Stored Program Device.

Outline

E N D

Presentation Transcript

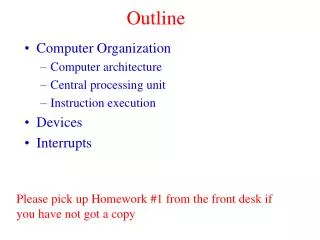

Outline • Computer Organization • Computer architecture • Central processing unit • Instruction execution • Devices • Interrupts Please pick up Homework #1 from the front desk if you have not got a copy

Review: System Overview COP4610

Pattern Jacquard Loom Variable Program Stored Program Device Stored Program Computers and Electronic Devices Fixed Electronic Device COP4610

Jacquard Loom COP4610

von Neumann Architecture COP4610

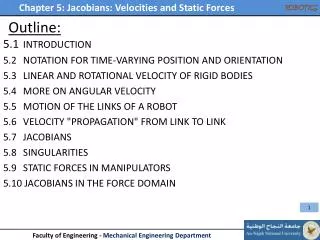

The von Neumann Architecture – cont. • A von Neumann architecture consists of • A central processing unit made up of ALU and control unit • A primary memory unit • I/O devices • Buses to interconnect the other components COP4610

von Neumann Architecture – cont. • The crucial difference between computers and other • electronic devices is the variable program COP4610

Central Processing Unit • Datapath • ALU – Arithmetic/Logic Unit • Registers • General-purpose registers • Control registers • Communication paths between them • Control • Controls the data flow and operations of ALU COP4610

S1 bus Dest bus S2 bus Control unit ALU A R0, r1,... (registers) C B ia(PC) psw... MAR MDR IR MAR memory address register MDR memory data register IR instruction register Memory

ALU Unit COP4610

Memory Organization COP4610

Instruction Execution • Instruction fetch (IF) MAR PC; IR M[MAR] • Instruction Decode (ID) A Rs1; B Rs2; PC PC + 4 • Execution (EXE) • Depends on the instruction • Memory Access (MEM) • Depends on the instruction • Write-back (WB) COP4610

Arithmetic Instruction Example • r3 r1 + r2 • IF: MAR PC; IR M[MAR] • ID: A r1; B r2; PC PC + 4 • EXE: ALUoutput A + B • MEM: • WB: r3 ALUoutput COP4610

S1 bus Dest bus S2 bus Control unit ALU A R0, r1,... (registers) C B ia(PC) psw... MAR MDR IR MAR memory address register MDR memory data register IR instruction register Memory

Memory Instruction Example • load 30(r1), r2 • IF: MAR PC; IR M[MAR] • ID: A r1; PC PC + 4 • EXE: MAR A + #30 • MEM: MDR M[MAR] • WB: r2 MDR COP4610

S1 bus Dest bus S2 bus Control unit ALU A R0, r1,... (registers) C B ia(PC) psw... MAR MDR IR MAR memory address register MDR memory data register IR instruction register Memory

Branch/jump Instruction Example • bnez r1, -16 • IF: MAR PC; IR M[MAR] • ID: A r1; PC PC + 4 • EXE: ALUoutput PC + #-16; cond (A op 0) • MEM: if (cond) PC ALUoutput • WB: r1 = 100 r4 = 0 r3 = 1 L1: r4 = r4 + r3 r3 = r3 + 2 r1 = r1-1 if (r1!=0) goto L1 // Outside loop // r4 ? COP4610

S1 bus Dest bus S2 bus Control unit ALU A R0, r1,... (registers) C B ia(PC) psw... MAR MDR IR MAR memory address register MDR memory data register IR instruction register Memory

Devices • I/O devices are used to place data into primary memory and to store its contents on a more permanent medium • Logic to control detailed operation • Physical device itself • Each device uses a device controller to connect it to the computer’s address and data bus • Many types of I/O devices COP4610

Device manager • Program to manage device controller • Supervisor mode software Application Program Software in the CPU Abstract I/O Machine Device Controller Device Devices – cont. COP4610

Devices – cont. • General device characteristics • Block-oriented devices • Character-oriented devices • Input devices • Output devices • Storage devices • Communication devices COP4610

Device Controllers • A hardware component to control the detailed operations of a device • Interface between controllers and devices • Interface between software and the controller • Through controller’s registers COP4610

busy done 0 0 idle 0 1 finished 1 0 working 1 1 (undefined) . . . busy done Error code . . . Command Status Data 0 Data 1 Logic Data n-1 Device Controllers – cont. COP4610

Communication Between CPU and Devices • Through busy-done flag • Called polling • A busy-waiting implementation • Not effective COP4610

… // Start the device … While(busy == 1) wait(); // Device I/O complete … done = 0; Software busy done Hardware … while((busy == 0) && (done == 1)) wait(); // Do the I/O operation busy = 1; … Polling I/O COP4610

Polling I/O – cont. • It introduces busy-waiting • The CPU is busy, but is effectively waiting • Devices are much slower than CPU • CPU waits while device operates • Would like to multiplex CPU to a different process while I/O is in process while(deviceNo.busy || deviceNo.done) <waiting>; deviceNo.data[0] = <value to write> deviceNo.command = WRITE; while(deviceNo.busy) <waiting>; deviceNo.done = TRUE; COP4610

A More Efficient Approach • When a process is waiting for its I/O to be completed, it would be more effective if we can let another process to run to fully utilize the CPU • It requires a way for the device to inform the CPU when it has just completed I/O COP4610

… … … Ready Processes Ready Processes Ready Processes CPU CPU CPU Device Device Device I/O Operation Uses CPU Better Utilization of CPU COP4610

Interrupts COP4610

Interrupt Handling – cont. COP4610

program Interrupt handler interrupt Interrupts – cont. COP4610

Interrupts – cont. • An interrupt is an immediate (asynchronous) transfer of control caused by an event in the system to handle real-time events and running-time errors • Interrupt can be either software or hardware • I/O device request (Hardware) • System call (software) • Signal (software) • Page fault (software) • Arithmetic overflow • Memory-protection violation • Power failure COP4610

Interrupts – cont. • Causes of interrupts: • System call (syscall instruction) • Timer expires (value of timer register reaches 0) • I/O completed • Program performed an illegal operation: • Divide by zero • Address out of bounds while in user mode • Segmentation fault COP4610

Synchronous vs. Asynchronous • Synchronous • Events occur at the same place every time the program is executed with the same data and memory • Can be predicted • Asynchronous • Caused by devices external to the processor or memory COP4610

Interrupt Handling • When an interrupt occurs, the following steps are taken • Save current program state • Context switch to save all the general and status registers of the interrupted process • Find out the interrupt source • Go to the interrupt handler COP4610

Interrupt Handling – cont. • Problem when two or more devices finish during the same instruction cycle • Race condition between interrupts COP4610

A Race Condition saveProcessorState() { for(i=0; i<NumberOfRegisters; i++) memory[K+i] = R[i]; for(i=0; i<NumberOfStatusRegisters; i++) memory[K+NumberOfRegisters+i] = StatusRegister[i]; } COP4610

Interrupt Handling – cont. • Race condition between interrupts • Interrupt-enabled flag COP4610

Trap Instruction COP4610

Signal in UNIX • Signal can be an asynchronous or synchronous event • For example, CTRL-C generates SIGINT • Divide-by-zero is a synchronous event • Signals sent to a process • Are handled by the operating system on behalf of the running process • The program can change the default action taken by the operating system for a particular signal • Function signal does not handle any signal by itself COP4610

Memory-mapped I/O • Instructions to access device controller’s registers • Special I/O instructions • Memory-mapped I/O COP4610

Addressing Devices Primary Memory Primary Memory Memory Addresses Device 0 Device 0 Memory Addresses Device 1 Device 1 Device Addresses Device n-1 Device n-1 COP4610

Intel System Initialization RAM Boot Prog ROM Loader Power Up Boot Device POST OS BIOS … CMOS Hardware Process Data Flow COP4610

0x0000100 BIOS loader Fetch Unit 0000100 PC Decode Unit IR … Execute Unit Bootstrapping Bootstrap loader (“boot sector”) 1 0x0001000 Primary Memory COP4610

Fetch Unit 0001000 PC Decode Unit IR … Execute Unit Bootstrapping – cont. Bootstrap loader (“boot sector”) 1 0x0000100 2 BIOS loader 0x0001000 0x0008000 Loader Primary Memory COP4610

Fetch Unit 0008000 PC Decode Unit IR … Execute Unit Bootstrapping Bootstrap loader (“boot sector”) 1 0x0000100 2 BIOS loader 0x0001000 0x0008000 Loader 3 0x000A000 OS Primary Memory COP4610

Bootstrap loader (“boot sector”) 1 0x0000100 2 BIOS loader 0x0001000 0x0008000 Fetch Unit Loader 3 000A000 PC 0x000A000 Decode Unit OS IR … Primary Memory Execute Unit 4. Initialize hardware 5. Create user environment 6. … Bootstrapping – cont. COP4610

A Bootstrap Loader Program FIXED_LOC: // Bootstrap loader entry point load R1, =0 load R2, =LENGTH_OF_TARGET // The next instruction is really more like // a procedure call than a machine instruction // It copies a block from FIXED_DISK_ADDRESS // to BUFFER_ADDRESS read BOOT_DISK, BUFFER_ADDRESS loop: load R3, [BUFFER_ADDRESS, R1] store R3, [FIXED_DEST, R1] incr R1 bleq R1, R2, loop br FIXED_DEST COP4610

A Pipelined Function Unit Operand 1 Function Unit Result Operand 2 (a) Monolithic Unit Operand 1 Result Operand 2 (b) Pipelined Unit COP4610

ALU Control Unit (a) Conventional Architecture ALU Control Unit ALU ALU … ALU (b) SIMD Architecture A SIMD Machine COP4610