SRAM Generator

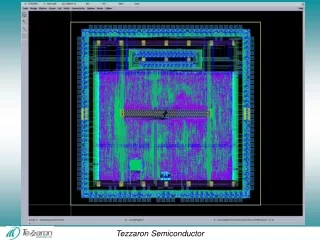

SRAM Generator. - Satya Nalam. SRAM specs Single bank Capacity – 8-32kb Col-mux – 1,2,4,8 #Rows – 8-512 #Rows and #cols power of 2 Timing block using encounter Schematic/Layout script for tiling each block Wrapper script to generate final SRAM. SRAM Architecture. Design. WLs. BLs.

SRAM Generator

E N D

Presentation Transcript

SRAM Generator - Satya Nalam

SRAM specs Single bank Capacity – 8-32kb Col-mux – 1,2,4,8 #Rows – 8-512 #Rows and #cols power of 2 Timing block using encounter Schematic/Layout script for tiling each block Wrapper script to generate final SRAM SRAM Architecture

Design WLs BLs Pre-decode o/p BL PCH CSEL Col-muxed BLs SAE SAPCH SA output Enable Address EN Rd/Wr Data in & out

Can be completely automated Parametrization Use @key in Skill procedures for optional arguments Transistor sizes from optimization result Schematic Generation procedure(UvaEceSchematicCreateInstParNand2(cvid libName cellName Iname location intop inbot out VDD VSS @key (lp 0.06) (wp 0.20) (ln 0.060) (wn 0.20) (m 1))

Schematic Generation • Leaf-cell schematic creation • Bitcells – PDK • Decoders – Skill • Everything else – Manual, can be replaced by Skill

Layout Generation: WLD WLD2 WLD1 • WL Drivers • Via-programmed • Staggered for pitch-matching

Layout Generation: Array Termination cells Well taps

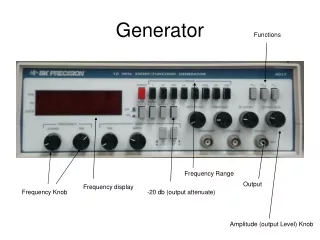

Layout Generation: Timing Predecode outputs Design placed and routed by Encounter

Layout Generation: Bitslice CD SA IO IO Staggered for pitch-matching

Layout Generation: Top-level 128x64 SRAM Routing through Abutment - Fillers with metal

Summary of useful tips for automation through Skill • Using procedures – with @key optional arguments • Via-programming • Staggering for pitch-matching • Routing through abutment

Final deliverable • Completed set of highly parametrized Skill scripts for SRAM schematic and layout generation. • Technology and user independent. • Class-specific work – parametrization of schematic and layout scripts • Documentation in progress.