SRAM Overview

SRAM Overview. SRAM Features Asynchronous vs. Synchronous Pipelined vs. Flow-Through Burst Mode Zero Bus Turnaround (ZBT). What is SRAM? Memory vs. Storage Terminology Static vs. Dynamic Random vs. Sequential. Address n. 0. 1. 1. 1. 1. 0. 1. 0. 1. 1. 1. 0. 0. 0. 1. 1.

SRAM Overview

E N D

Presentation Transcript

SRAM Features Asynchronous vs. Synchronous Pipelined vs. Flow-Through Burst Mode Zero Bus Turnaround (ZBT) What is SRAM? Memory vs. Storage Terminology Static vs. Dynamic Random vs. Sequential Address n 0 1 1 1 1 0 1 0 1 1 1 0 0 0 1 1 1 0 0 0 0 0 1 1 1 1 1 1 1 0 0 0 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 0 Address 0 1 2 3 4 5 6 7 8 Objectives

Memory vs. Storage • Memory • Volatile • Fast Access • Storage • Non-volatile • Large Capacity • Slower Access

. Address n . . Address 1 1 1 0 1 0 0 1 0 Address 0 1 2 3 4 5 6 7 8 BIT 0 1 1 1 1 0 1 0 1 1 0 0 1 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 0 0 1 1 1 1 0 1 0 0 0 Terminology • Bits • Bytes • Density • Width • Depth • Speed Depth Width

READ WRITE 0 0 0 0 0 0 1 1 1 1 0 0 1 1 0 0 Memory Read & Write

Access Time (Speed) Data Read / Written Request Read / Write Time Access Time

Dynamic Static Refresh Static vs. Dynamic

0 1 0 0 0 0 1 1 0 0 1 0 1 1 1 1 0 0 1 1 1 1 1 1 0 0 1 0 1 1 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 0 0 0 1 0 0 1 0 1 0 0 0 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 0 1 0 0 0 1 0 0 0 1 0 0 0 0 ADDRESS Control DATA Control DATA Random vs. Sequential • Random Access Memory • Sequential Access Memory

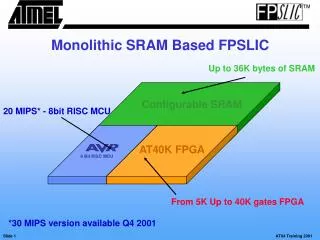

ADDRESS SRAM 4 M 512K X 8 Control DATA Static Random Access Memory

Clock Addr /Cntrl CPU SRAM Data Clock Addr /Cntrl CPU SRAM Data Asynchronous vs. Synchronous • Asynchronous SRAM • CPU controls all memory timing • Synchronous SRAM • Clock controls memory timing • CPU enables

Memory Cells Data Out Register Memory Cells Data Out Data Pipelined vs. Flow-Through • Flow-Through • Pipelined

SRAM Non-Burst Mode Address a Data (a) SRAM Burst Mode Address a Data (a) Data (b) Data (c) Data (d) Burst Mode • Non-Burst Mode • Burst Mode

Bus Turnaround from Write to Read SRAM Data Bus Write Idle Idle Read Idle ZBT SRAM Data Bus Write Read Write Read Write No idle time between Reads and Writes Zero Bus Turnaround (ZBT)

Summary • Terminology • Data storage types • SRAM features ADDRESS SRAM 4 M 512K X 8 Control DATA