Computer Organization

70 likes | 134 Views

Chapter 6 : ARITHMETIC. Computer Organization. Department of CSE, SSE Mukka. Addition and Subtraction of signed numbers. Sum s i can be implemented with XOR gate. Carry-out function c i+1 can be implemented with a two-level AND-OR logic circuit.

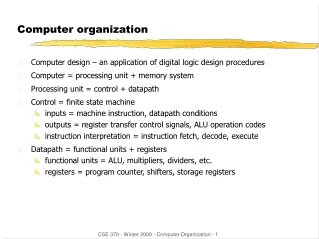

Computer Organization

E N D

Presentation Transcript

Chapter 6 : ARITHMETIC Computer Organization Department of CSE, SSE Mukka www.bookspar.com | Website for students | VTU NOTES

Addition and Subtraction of signed numbers • Sum si can be implemented with XOR gate. • Carry-out function ci+1 can be implemented with a two-level AND-OR logic circuit. • A cascaded connection of n full adder blocks can be used to add two n-bit numbers – called as n-bit ripple carry adder • The carry-in C0 into least significant-bit position provides a convenient means of adding 1 to a number • For example forming 2’s complement of a number involves adding 1 to 1’s complement of the number www.bookspar.com | Website for students | VTU NOTES

x y Carry-in c Sum s Carry-out c i i i i i +1 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 x y c + x y c + x y c + x y c s = = x Å y Å c i i i i i i i i i i i i i i i i y c x c x y c = + + i i i i i i i +1 E xample: x X 7 0 1 1 1 Carry-out Carry-in i y + Y = + 6 = + 0 1 1 0 0 1 1 0 0 c i c i +1 i Z 13 1 1 0 1 s i Legend for stage i Figure 6.1.Logic specification for a stage of binary addition. www.bookspar.com | Website for students | VTU NOTES

y i c i x i x i c y s c i i i + 1 i c i x x y i i i y i Full adder c c i + 1 i (F A) s i (a) Logic f or a single stage x y x y x y n - 1 n - 1 1 1 0 0 c c n - 1 1 c c F A F A F A n 0 s s s n - 1 1 0 Most significant bit Least significant bit (MSB) position (LSB) position (b) An n -bit r ipple-carr y adder x y x y x y x y x y k n - 1 k n - 1 2 n - 1 2 n - 1 n n n - 1 n - 1 0 0 c n n - bit n - bit n - bit c c adder adder adder 0 k n s s s s s s ( ) k n - 1 k - 1 n 2 n - 1 n n - 1 0 (c) Cascade of k n-bit adders Figure 6.2. Logic for addition of binary vectors. www.bookspar.com | Website for students | VTU NOTES

y y y n - 1 1 0 Add/Sub control x x x n - 1 1 0 n -bit adder c n c 0 s s s n - 1 1 0 Figure 6.3. Binary addition-subtraction logic netw ork. www.bookspar.com | Website for students | VTU NOTES

y x i i . . . c i B cell G P s i i i (a) Bit-stage cell x y x y x y x y 3 3 2 2 1 1 0 0 . c c c c 3 2 1 c B cell B cell B cell B cell 4 0 s s s s 3 2 1 0 G P G P G P G P 0 0 3 3 2 2 1 1 Carry-lookahead logic I I G P 0 0 (b) 4-bit adder Figure 6.4. 4-bit carry-lookahead adder. www.bookspar.com | Website for students | VTU NOTES

x y x y x y x y 15-12 15-12 11-8 11-8 7-4 7-4 3-0 3-0 . c c c 12 8 4 4-bit adder c 4-bit adder 4-bit adder c 4-bit adder 16 0 s s s s 15-12 11-8 7-4 3-0 I I I I I I G P G P G P G I P I 3 3 2 2 1 1 0 0 Carry-lookahead logic II II G P 0 0 Figure 6.5. 16-bit carry-lookahead adder built from 4-bit adders www.bookspar.com | Website for students | VTU NOTES