Very Simple Computer Organization

Learn about the Very Simple Computer system, its architecture, functional units, instructions, register transfers, hardware implementation, and the VSC assembler for programming. Includes detailed design information and examples.

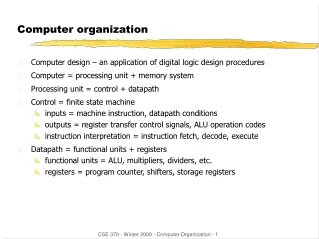

Very Simple Computer Organization

E N D

Presentation Transcript

Computer Organization CSC 405 (VSC) Very Simple Computer

Very Simple Computer (VSC) The VSC is a very impractical computer system with a single Bus, a 32 8-bit Word memory, switch/LED input/output, supporting 8 instructions. As simple as it is, the VSC is a complete representation of the Von Neumann Architecture. Registers: PC - program counter IR - instruction register MAR - memory address register LAT1 - latch 1, ALU input register LAT2 - latch 2, ALU input register ACC - accumulator, ALU output register VSC Functional Units: I/O - input output unit CU - control unit MU - memory unit ALU - arithmetic/logic unit For detailed design information on the VSC, please read the Very Simple Computer Overview.

A Walk through the Fetch/Execute Cycle MAR <- PC IR <- MEM[MAR] PC <- PC+1 MAR <- IR0-4 LAT1 <- MEM[MAR] LAT2 <- ACC EXEen

The Instructions of the VSC The eight instructions of the VSC are based on the Post/Turing language. These instructions form a complete set of operations. While not very practical, the operations of the Post/Turing language can be used to emulate any computable function. LDA - load the accumulator with a word from memory (selected by MAR) STA - store the word in the accumulator into memory (at address in MAR) ADD - add LAT1 and LAT2 and store the result into the accumulator (ACC) CMP - complement (bit inverse) the value in LAT1 and store in accumulator BNN - if the MSB of ACC is zero (0) replace PC with address in IR SHL - perform an arithmetic shift left on the value in LAT1 SHR - perform an arithmetic shift right on the value in LAT1 HLT - stop the fetch/execute cycle (for VSC set PC to 11111)

OpCode ASM Register Transfer 000 LDA ACC <- MEM[MAR] 001 STA MEM[MAR] <- ACC 010 ADD ACC <- LAT1+LAT2 011 CMP ACC <- LAT1 100 BNN IF ACC7=0 THEN PC <- IR0-4 101 SHL ACC <- 2*LAT1 110 SHR ACC <- LAT1/2 111 HLT PC <- 11111 Register Transfers for Instruction Executions There is a different register transfer operation for each of the eight instructions of the VSC. The Control Unit is a combinatorial circuit (encoder) that activates the read and write enable lines that correspond to the operation indicated by the OpCode.

0 1 2 3 4 5 6 7 MARRE PCRE PCWE PCINC IRRE IRWE LAT1RE LAT2RE MEMRE MEMWE ACCRE ACCWE EXEEN start 000 111 001 010 110 101 011 100 Time Implementing the Register Transfers in Hardware We have defined the registers for the VSC, the functional blocks (units) and the logic for the fetch/execute cycle. Now we need to design the circuitry that will invoke these register transfers. There are 7 steps in the fetch/execute cycle. We will use a divide-by-eight counter to generate the Read and Write enable signals for each step. 1 MAR <- PC 2 IR <- MEM[MAR] 3 PC <- PC+1 4 MAR <- IR0-4 5 LAT1<- MEM[MAR] 6 LAT2<- ACC 7 EXEen 8 No Op

The clock pulses that drive the divide-by-eight counter can be produced with a timer circuit (built from a mA555). The divide-by-eight counter is available in a single TTL IC (7493). The 3-to-8 decoder can be built by inverting the outputs of a popular decoder IC (74138). 555 Timer 0 1 2 3 4 5 6 7 3-to-8 Decoder Divide by 8 Counter MARRE PCRE PCWE PCINC IRRE IRWE LAT1RE LAT2RE MEMRE MEMWE ACCRE ACCWE EXEEN

IR OpCode OpCode ASM Register Transfer 000 LDA ACC <- MEM[MAR] 001 STA MEM[MAR] <- ACC 010 ADD ACC <- LAT1+LAT2 011 CMP ACC <- LAT1 100 BNN if ACC7=0 then PC<-IR0-4 101 SHL ACC <- 2*LAT1 110 SHR ACC <- LAT1/2 111 HLT PC <- 11111 3-to-8 Decoder ACC7 ACCRE ACCWE MEMRE MEMWE PCRE IRWE ADDEN CMPEN SHLEN SHREN HLT MEMRE MEMRE MEMRE 7 6 5 4 3 2 1 0 A similar circuit can be built to generate the control signals needed to implement each of the eight instructions of the VSC. In this case, the control lines input to the 3-to-8 decoder come directly from the OpCode of the current instruction in IR5-7. Note: Enable lines in common with those in the fetch circuit must be connected through OR gates.

VSC ASM Addr Data/Instr LDA X 00000 00000100 ADD Y 00001 01000101 STA Z 00010 00100110 HLT 00011 11111111 X 6 00100 00000110 Y 3 00101 00000011 Z 0 00110 00000000 We can define an assembler to write programs for the VSC. This assembler will be used to help us manually develop machine code (1’s and 0’s) for the VSC. The best way to become familiar with the VSC assembler is by reviewing a few examples: In our first example we will write a program to add the values 6 and 3. We will preload these values into memory labeled X and Y and have the program store the result in Z. Note that the assembly language commands are simply the 8 operations we defined for the VSC and their corresponding op-codes are the 3 highest-order bits of each instruction. The program is placed in memory with the 1st instruction at address 0000. Upon completion the VSC should hold the value 00001001 at memory address 00110.

The next example is a program that checks an input value X. If X is even then it is divided by 2 otherwise it is multiplied by 2. The result replaces X. In this example X=7. LDA X 00000 00010001 SHR 00001 11000000 SHL 00010 10100000 STA Y 00011 00110010 LDA X 00100 00010001 CMP 00101 01100000 ADD ONE 00110 01010011 ADD Y 00111 01010010 BNN EVEN 01000 10001101 LDA X 01001 00001111 ODD SHL 01010 10100000 LDA ZERO 01011 00010100 BNN SAVE 01100 10001111 EVEN LDA X 01101 00010001 SHR 01110 11000000 SAVE STA X 01111 00110001 HLT 10000 11111111 X [INPUT] 10001 00000111 Y 0 10010 00000000 ONE 1 10011 00000001 ZERO 0 10100 00000000 First the value of X is loaded into the accumulator. Then it is divided and multiplied by 2. The value of X is subtracted from this result (Y). If the difference is negative then X was odd so X is loaded and multiplied by 2. The program then jumps to the address labeled SAVE. If the difference is zero (i.e. not negative) then X was even so X is loaded and divided by 2. The program then saves the result back into X. Homework: Write a VSC assember program that computes the sum of the first 10 integers. Use the pseuodo-code as shown in the last two examples.