FPGA Technology Overview

FPGA Technology Overview. Carl Lebsack. * Some slides are from the “Programmable Logic” lecture slides by Dr. Morris Chang. What’s an FPGA?. FPGA – Field Programmable Gate Array. Logic. Standard Logic. ASIC. Gate Arrays. Programmable Logic Devices. Cell-Based ICs. Full custom ICs.

FPGA Technology Overview

E N D

Presentation Transcript

FPGA Technology Overview Carl Lebsack * Some slides are from the “Programmable Logic” lecture slides by Dr. Morris Chang

What’s an FPGA? FPGA – Field Programmable Gate Array

Logic Standard Logic ASIC Gate Arrays Programmable Logic Devices Cell-Based ICs Full custom ICs FPICs SPLDs CPLDs FPGAs

How do you make a “Programmable” circuit? • One time programmable • Fuses (destroy internal links with current) • Anti-fuses (grow internal links) • PROM • Reprogrammable • EPROM • EEPROM • Flash • SRAM - volatile } non-volatile

How do you program an FPGA? • Create a circuit design • Graphic circuit tool • Verilog • VHDL • AHDL • Compile the design for the selected device • Download the compiled configuration

FPGAs offer many advantages over ASICs • Small development overhead • No NRE (non-recurring engineering) costs • Quick time to market • No minimum quantity order • Reprogrammable

What are the Guts of an FPGA? • Basic Components • LUT (look-up-table) • Flip-Flops • Multiplexors • I/O Blocks • Programmable switching matrices • Interconnect • Clocks

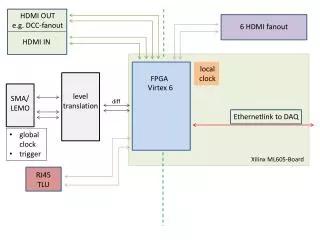

Xilinx FPGA Structure Configurable Logic Blocks I/O Blocks Programmable Interconnects

config_out input[0:2] 0 1 1 0 1 0 0 1 output clock config_in 3-LUT

More Guts • Additional components • RAM blocks • Dedicated multipliers • Tri-state buffers • Transceivers • Processor cores • DSP blocks

Dedicated Arithmetic Structures in FPGAs QuickLogic Altera Xilinx

Power PC in Virtex-II Pro • Embedded 300+ MHz Harvard Architecture Core • • Low Power Consumption: 0.9 mW/MHz • • Five-Stage Data Path Pipeline • • Hardware Multiply/Divide Unit • • Thirty-Two 32-bit General Purpose Registers • • 16 KB Two-Way Set-Associative Instruction Cache • • 16 KB Two-Way Set-Associative Data Cache • • Memory Management Unit (MMU) • - 64-entry unified Translation Look-aside Buffers (TLB) • - Variable page sizes (1 KB to 16 MB) • • Dedicated On-Chip Memory (OCM) Interface • • Supports IBM CoreConnect™ Bus Architecture • • Debug and Trace Support • • Timer Facilities

Excalibur Embedded Solution • Integrates Embedded Processors With Programmable Logic Device • Delivers System-on-a-Programmable-Chip (SOPC) • Programmable Flexibility • PLD Hardware • Embedded Software • Compute Performance • High Performance Processor • Data Path Hardware • Customer Configuration • Microprocessor Peripherals • Hardware Logic • Faster Time-to-Market Excalibur Processor Memory High Performance I/O Logic Complete SOPC Solution

ARM in Excalibur • Industry-standard ARM922T 32-bit RISC processor core operating up to 200MHz • ARMv4T instruction set with Thumb extensions • Memory management unit (MMU) included for real-time operating systems (RTOS) support • Harvard cache architecture with 64-way set associative separate 8-Kbyte instruction and 8-Kbyte data caches • Embedded programmable on-chip peripherals • ETM9 embedded trace module to assistant software debugging • Flexible interrupt controller • Universal asynchronous receiver/transmitter (UART) • General-purpose timer • Watchdog timer

Xilinx Slices/CLBs PowerPC cores Altera LEs/LABs ARM cores/Softcores FPGAs come in a wide variety Numbers of subcomponents varies Special features vary Manufacturers use own terminology

FPGA Design • Main components are generally done as custom designs • Layout is very regular and automation could assist in cell placement

PLD device density and VLSI technology *note: Xilinx Virtex-II Pro XC2VP100 (9/16/2003)

More Information • www.xilinx.com • www.altera.com