ECE-301 Midterm Results and Upcoming Course Objectives Overview

The results for the ECE-301 midterm exam are in, with 57 out of 60 students participating. The class average was 77.9, with a median of 78, showing a reasonable distribution of scores ranging from 36 to 100. All students will receive a 5-point adjustment to their scores. As we plan for the remainder of the course, we will dive into combinational and sequential circuits, programmable logic devices, and related topics. This week’s focus will include half adders, full adders, code conversion, and analysis techniques. Remember to seek assistance during office hours if needed!

ECE-301 Midterm Results and Upcoming Course Objectives Overview

E N D

Presentation Transcript

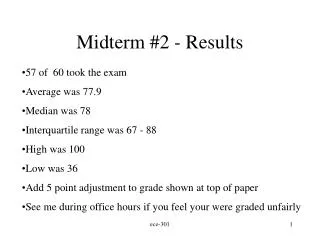

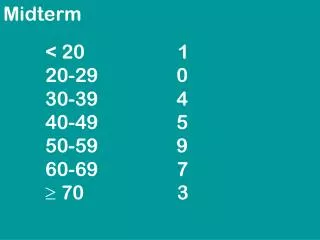

Midterm #2 - Results • 57 of 60 took the exam • Average was 77.9 • Median was 78 • Interquartile range was 67 - 88 • High was 100 • Low was 36 • Add 5 point adjustment to grade shown at top of paper • See me during office hours if you feel your were graded unfairly ece-301

Where are we now? • 7 weeks down; 7 weeks to go • Starting week #9 (March 20, 2000) • Basic tools are in the bag (let’s use them) • Hope to finish combinational circuits this week (at least try) • Plan to attack “sequential” circuits after that (ie. FEEDBACK) • Then: Programmable Logic Devices / Decoders / Flip-Flops / • State Diagrams / Registers / Counters / RAM / etc. ece-301

Objectives for Week #9 • Half adders • Full adders • Subtractors • Design vs. Analysis • Code conversion • Analysis by (1) truth table, (2) Boolean expression • Multi-level NANDS and multi-level NORS • Exclusive OR (parity generation and checking) ece-301

Assignment for week #9 (3/20/00) • Reading: 20 Mar: 4-4 to 4-6; 22 Mar: 4-7 to 4-9 • Homework Problems (HW#9); Ch 4: 17, 18, 23 • due Monday, 27 Mar 00 ece-301

Exam Philosophy (for free) • This is a course in logic more than it is digital design • Understand the question before you provide an answer • Give the grader half a chance of interpreting your work • Concentrate on the heavily weighted questions • don’t get sloppy with x’s and y’s and with prime marks • if you can’t deduce the answer, at least make a stab at it • And when you get a job: remember that communication is everything. Also, employers don’t like to give “partial credit”. . . They want the right answer. ece-301

More philosophy • Employers are looking for logical reasoning and application of principles to new situations . . . Not just regurgitation. • Finally, give your answer a verification check; does it pass the common sense test? ece-301

Subtractors • Author uses “brute strength and awkwardness approach (ie doesn’t use complements) • half subtractor: x, y, B, D • D = x`y + xy` (ah hah . . . An exclusive OR) • B = x`y (note: same as logic for S on a half-adder) • Full subtractor: x, y, z, B, D (where z is the previous borrow) • D = x`y`z + x`yz` + xy`z` + xyz • B = x`y + x`z + yz ece-301

Code Conversion • Author uses example of “Excess-3” code (see page 18) • Could be any other code • It’s a translator (say French to Spanish) • Number of inputs = Number of outputs • Make a truth table; then a Karnaugh map; then simplify; then implement in a logic diagram (usually use AND-OR-INVERT(gates) • Might later convert to NOR implementation or NAND implementation. ece-301

Very short course on transistors • Halfway between conductors and insulators • grow a very pure icicle of silicon • “dope” it (ie, poison it) with slight impurity (boron, antimony) to give it either “p” or “n” characteristic • IC’s usually fabricated by vacuum deposition • use precisely positioned masks to assure the etching occurs at proper place • connection “wires” are pretty thin: like one nanometer • that’s a meter divided by 1000, divided by 1000, divided by 1000. ece-301

Analysis Procedure (4-6) • Start with a logic diagram • two approaches: (1) Boolean, or (2) Truth Table • It’s all common sense; stuff you’ve done before • label the outputs of all gates; work from left to right; derive intermediate gate outputs in terms of known variables • you’re done when you arrive at the right hand side, and all labels are identified in terms of the input variables • Or, just skip the above and go directly to a truth table; but you still have to identify intermediate gate outputs. ece-301

Multilevel NAND circuits • NAND is a universal gate (you can build anything from them) • you can construct OR, AND, INVERT gates from NANDS • multilevel means two or more • start with a logic diagram in AND-OR or OR-AND • work from right to left • best to have AND-OR in alternate levels • should be able to also go from multilevel NAND to AND-OR in multiple levels ece-301