Liaison Report JEDEC JC-61

60 likes | 226 Views

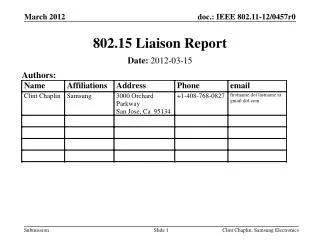

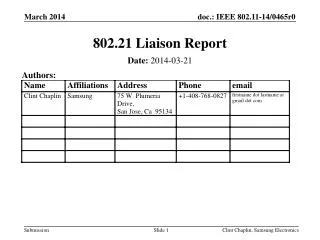

Liaison Report JEDEC JC-61. Benno Ritter Philips September 13 th 2002. Status. Currently 42 member companies with a total of >120 participating members and alternates Last meeting in Sunnyvale, CA on September 5th and 6th 22 participating companies

Liaison Report JEDEC JC-61

E N D

Presentation Transcript

Liaison Report JEDEC JC-61 Benno Ritter Philips September 13th 2002 Benno Ritter, Philips

Status • Currently 42 member companies with a total of >120 participating members and alternates • Last meeting in Sunnyvale, CA on September 5th and 6th • 22 participating companies • Next meeting in July 7th – 8th in Koloa, HI before the IEEE meeting (same hotel) www.jedec.org • Documents finished: • Procedure and Operating Rules • MRD for both interface • TRD for both interfaces • Welcome Information Package Benno Ritter, Philips

Current Proposals • RF – BB Interface • Philips (PHY of Serial ATA) • Channel Technologies (6 line digital differential) • nVidea (8 line digital differential) • MAC – PHY Interface • Channel Technologies (6 line digital differential) Benno Ritter, Philips

Characteristics • All proposals • High speed serial data • Differential ( for >50cm distance ) • Data rates in the order of 1.2 – 1.6 Gbps • Extension to higher data rates by adding lines • Protocols are very similar • Differences • Embedded versus separate clock (additional lines) • 3 of PLLs • Reusability of existing IP blocks • Clock frequency • Necessary logic for data packetizing/de-packetizing Benno Ritter, Philips

Next Steps • Discuss system implications of embedded versus non-embedded clock • Continue to foster merger opportunities • Clarification of IP situation for proposals • Ballot on clocking scheme Leads to baseline proposal before the November meeting Benno Ritter, Philips

Proposed Timeline Q2’02 Q3’02 Q4’02 Q1’03 Public Call for Proposals Approve MRD & TRD Review Proposals Select Idea by Vote Match Idea to MRD/TRD Create Written Standard Approve Standard Benno Ritter, Philips