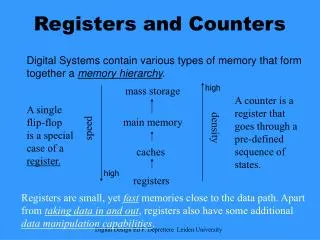

Registers and Counters

Registers and Counters. Discussion D8.1. Logic Design Fundamentals - 3. Registers Counters Shift Registers. A 1-Bit Register. Behavior. if rising_edge(CLK) then if LOAD = ‘1’ then Q0 <= INP0; end if; end if;. A 4-Bit Register. A Generic Register. library IEEE;

Registers and Counters

E N D

Presentation Transcript

Registers and Counters Discussion D8.1

Logic Design Fundamentals - 3 • Registers • Counters • Shift Registers

A 1-Bit Register Behavior if rising_edge(CLK) then if LOAD = ‘1’ then Q0 <= INP0; end if; end if;

A Generic Register library IEEE; use IEEE.std_logic_1164.all; entity reg is generic(width: positive); port ( d: in STD_LOGIC_VECTOR (width-1 downto 0); load: in STD_LOGIC; clr: in STD_LOGIC; clk: in STD_LOGIC; q: out STD_LOGIC_VECTOR (width-1 downto 0) ); end reg;

architecture reg_arch of reg is begin process(clk, clr) begin if clr = '1' then for i in width-1 downto 0 loop q(i) <= '0'; endloop; elsif (clk'event and clk = '1') then if load = '1' then q <= d; end if; end if; end process; end reg_arch; Infers a flip-flop for all outputs (q)

A Generic Register with an initial value of 0 - 3 entity regr is generic(width: positive; bit0: std_logic; bit1: std_logic); port ( d: in STD_LOGIC_VECTOR (width-1 downto 0); load: in STD_LOGIC; reset: in STD_LOGIC; clk: in STD_LOGIC; q: out STD_LOGIC_VECTOR (width-1 downto 0) ); end regr;

A Generic Register with an initial value of 0 - 3 architecture regr_arch of regr is begin process(clk, reset) begin if reset = '1' then q <= (others => '0'); q(0) <= bit0; q(1) <= bit1; elsif (clk'event and clk = '1') then if load = '1' then q <= d; end if; end if; end process; end regr_arch;

count3 clr q(2 downto 0) clk 3-Bit Counter signal count: STD_LOGIC_VECTOR (2 downto 0); Behavior if clr = '1' then count <= "000"; elsif rising_edge(clk) then count <= count + 1; end if; Q <= count;

count3.vhd library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.STD_LOGIC_unsigned.all; entity count3 is port( clk : in STD_LOGIC; clr : in STD_LOGIC; q : out STD_LOGIC_VECTOR(2 downto 0) ); end count3; architecture count3 of count3 is signal count: STD_LOGIC_VECTOR(2 downto 0); begin process(clr,clk) begin if clr = '1' then count <= "000"; elsif clk'event and clk = '1' then count <= count + 1; end if; end process; q <= count; end count3; Need signal because q can not be read Asynchronous clear Signal count increments on rising edge of clk

Clock Divider mclk = 50 MHz master clock signal clk, cclk: std_logic; signal clkdiv: std_logic_vector(23 downto 0); begin -- Divide the master clock (50Mhz) down to a lower frequency. process (mclk) begin if mclk = '1' and mclk'event then clkdiv <= clkdiv + 1; end if; end process; clk <= clkdiv(0); -- mclk/2 = 25 MHz cclk <= clkdiv(17); -- mclk/218 = 190 Hz

4-Bit Shift Register s(0) s(3) s(2) s(1) Behavior if rising_edge(CLK) then for i in 0 to 2 loop s(i) := s(i+1); end loop; s(3) := data_in; end if;

library IEEE; use IEEE.STD_LOGIC_1164.all; entity shift4 is port( data_in : in STD_LOGIC; clk : in STD_LOGIC; clr : in STD_LOGIC; Q : out STD_LOGIC_VECTOR(3 downto 0) ); end shift4; architecture shift4 of shift4 is begin process(clr,clk) variable s: STD_LOGIC_VECTOR(3 downto 0); begin if clr = '1' then s := "0000"; elsif clk'event and clk = '1' then for i in 0 to 2 loop s(i) := s(i+1); end loop; s(3) := data_in; end if; Q <= s; end process; end shift4; shift4.vhd

Ring Counter s(0) s(3) s(2) s(1) Behavior Note: Must use signals here if rising_edge(CLK) then for i in 0 to 2 loop s(i) <= s(i+1); end loop; s(3) <= s(0); end if;

library IEEE; use IEEE.STD_LOGIC_1164.all; entity ring4 is port( clk : in STD_LOGIC; reset : in STD_LOGIC; Q : out STD_LOGIC_VECTOR(3 downto 0) ); end ring4; architecture ring4 of ring4 is signal s: STD_LOGIC_VECTOR(3 downto 0); begin process(reset,clk) begin if reset = '1' then s <= "0001"; elsif clk'event and clk = '1' then for i in 0 to 2 loop s(i) <= s(i+1); end loop; s(3) <= s(0); end if; end process; Q <= s; end ring4; ring4.vhd Note: Must use signals here

A Random Number Generator s(0) s(3) s(2) s(1) Behavior if rising_edge(CLK) then for i in 0 to 2 loop s(i) <= s(i+1); end loop; s(3) <= s(0) xor s(3); end if;

Q3 Q2 Q1 Q0 0 0 0 1 1 1 0 0 0 8 1 1 0 0 C 1 1 1 0 E 1 1 1 1 F 0 1 1 1 7 1 0 1 1 B 0 1 0 1 5 Q3 Q2 Q1 Q0 1 0 1 0 A 1 1 0 1 D 0 1 1 0 6 0 0 1 1 3 1 0 0 1 9 0 1 0 0 4 0 0 1 0 2 0 0 0 1 1

library IEEE; use IEEE.STD_LOGIC_1164.all; entity rand4 is port( clk : in STD_LOGIC; reset : in STD_LOGIC; Q : out STD_LOGIC_VECTOR(3 downto 0) ); end rand4; architecture rand4 of rand4 is signal s: STD_LOGIC_VECTOR(3 downto 0); begin process(reset,clk) begin if reset = '1' then s <= "0001"; elsif clk'event and clk = '1' then for i in 0 to 2 loop s(i) <= s(i+1); end loop; s(3) <= s(0) xor s(3); end if; end process; Q <= s; end rand4; rand4.vhd

clock_pulse library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_arith.all; entity clock_pulse is port ( inp, cclk, clr: in std_logic; outp: out std_logic ); end clock_pulse;

architecture clock_pulse_arch of clock_pulse is signal delay1, delay2, delay3: std_logic; begin process(cclk, clr) begin if clr = '1' then delay1 <= '0'; delay2 <= '0'; delay3 <= '0'; elsif cclk'event and cclk='1' then delay1 <= inp; delay2 <= delay1; delay3 <= delay2; end if; end process; outp <= delay1 and delay2 and (not delay3); end clock_pulse_arch; clock_pulse