Cache Memory

Cache Memory. Exercises. Questions I. Given: memory is little-endian and byte addressable; memory size; number of cache blocks, size of cache block An instruction lw $t0, x or lbu $t0, x; Determine HIT or MISS? What value is in $t0?; and Show the cache after word is brought in if needed.

Cache Memory

E N D

Presentation Transcript

Cache Memory Exercises

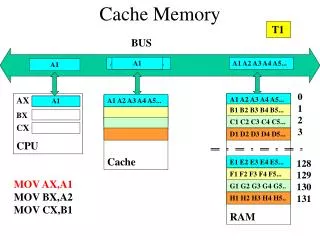

Questions I • Given: • memory is little-endian and byte addressable; memory size; • number of cache blocks, size of cache block • An instruction lw $t0, x or lbu $t0, x; • Determine • HIT or MISS? • What value is in $t0?; and • Show the cache after word is brought in if needed

Assume memory is little-endian and byte addressable; cache block = 1 word; Cache holds 4 blocks of data ( 4 words) 00 01 10 11 lbu $t0, x # x = 001101 Question 1: cache HIT or MISS? What is in $t0? Draw the cache after data is brought in

Assume memory is little-endian and byte addressable; cache block = 1 word; Cache holds 4 blocks of data ( 4 words) 00 01 10 11 lbu $t0, x # x = 001010 Question 2: cache HIT or MISS? What is in $t0? Draw the cache after data is brought in

Assume memory is little-endian and byte addressable; cache block = 1 word; Cache holds 4 blocks of data ( 4 words) 00 01 10 11 lbu $t0, x # x = 000111 Question 3: cache HIT or MISS? What is in $t0? Draw the cache after data is brought in

Assume memory is little-endian and byte addressable; cache block = 1 word; Cache holds 4 blocks of data ( 4 words) 00 01 10 11 lbu $t0, x # x = 010010 Question 4: cache HIT or MISS? What is in $t0? Draw the cache after data is brought in

Assume memory is little-endian and byte addressable; cache block = 1 word; Cache holds 4 blocks of data ( 4 words) 00 01 10 11 lbu $t0, x # x = 011011 Question 5: cache HIT or MISS? What is in $t0? Draw the cache after data is brought in

Cache Question II-1 • Suppose: 256 bytes of memory, cache holds 4 blocks, each block is 1 word. What is the cache size? • Answer: aaaaaaaa t t t t i i o o cache: valid tag data Cache size: 1 4 32 (4+1+32)*4 bits

Cache Question II-2 • Suppose: 256 bytes of memory, cache holds 8 blocks , each block is 1 word. What is the cache size? • Answer: aaaaaaaa t t t i i i o o cache: valid tag data Cache size: 1 3 32 (3+1+32)*8 bits

Question II-3 • What is the cache size (total number of bits) for a cache that holds 64KB of data (block == 1 word; 2**32 bytes of memory) • Answer: • 64KB == 16K words; • 16K = (2**4) *(2**10) = 2**14 • So 14 bits are needed for the cache index • Tag size = 32 – 14 -2 = 16 bits • Cache size = (1 + (32-14-2) + 32) * (2**14) = 784 K bits = 98 KB