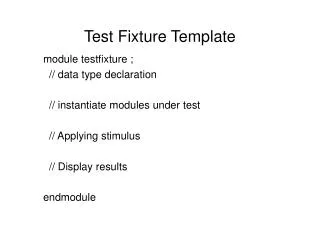

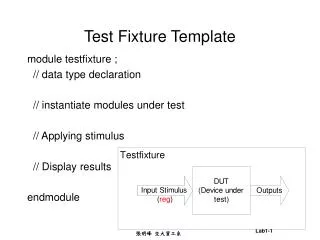

Test Fixture Template

Test Fixture Template. module testfixture ; // data type declaration // instantiate modules under test // Applying stimulus // Display results endmodule. Test Fixture - Data Type Declaration. module testfixture ; // data type declaration

Test Fixture Template

E N D

Presentation Transcript

Test Fixture Template module testfixture ; // data type declaration // instantiate modules under test // Applying stimulus // Display results endmodule

Test Fixture - Data Type Declaration module testfixture ; // data type declaration reg a, b, sel ; // the inputs of Device Under Test // instantiate modules under test // Applying stimulus // Display results endmodule

Test Fixture - Instantiate module testfixture ; // data type declaration reg a, b, sel ; // the inputs of Device Under Test // instantiate modules under test mux2_1 u1 (out, a, b, sel) ; // Applying stimulus // Display results endmodule

Test Fixture - Stimulus module testfixture ; // data type declaration reg a, b, sel ; // the inputs of Device Under Test // instantiate modules under test mux2_1 u1 (out, a, b, sel) ; // Applying stimulus using an initial block initial begin a=0 ; b=1 ; sel=0 ; #5 b=0 ; #5 b=1 ; sel=1 ; end // Display results endmodule

Display results //Display results initial begin $display(" time out a b sel"); $monitor($time, " %b %b %b %b", out,a,b,sel) ; end // Generate waveform initial begin $shm_open("mux.shm"); $shm_probe("AS"); end

Lab 1: Verilog for Combinational Ckts • Set up workstation environment • .cshrc • Cadence on-line manual • openbook • Verilog-XL User Guide • Verilog-XL Reference • Verilog-XL Tutorial • Two simple examples • 2-to-1 multiplexor (structural) • 3-to-8 decoder • Verilog simulation and simwave

7-segment decoder • input [3:0] in; • output a,b,c,d,e,f ; • Active low • RTL description • always block • Always @ (in) • a test fixture • print out waveform

4-bit magnitude comparator • input [3:0] a, b ; • input agb, alb, aeb ; • output agbo, albo, aebo ; • RTL description • Check inputs with high priority first • quiz