中斷 (Interrupt)

中斷 (Interrupt). 何為中斷 (Interrupt) ? 通常被定義為一種事件,可以改變處理器執行指令的順序。 為什麼要使用中斷 ? 通知 CPU 事件發生好執行相對應的動作。. 中斷 (Interrupt). 現代電腦硬體結構. 中斷 (Interrupt). 輪詢 (Polling) CPU 需隨時監看其他週邊 中斷 (Interrupt) 其他週邊告知 CPU 已完成工作. 中斷 (Interrupt). 輪詢 (Polling) 主單元輪流詢問從屬單元的狀態. 中斷 (Interrupt). 中斷 (Interrupt)

中斷 (Interrupt)

E N D

Presentation Transcript

中斷(Interrupt) • 何為中斷(Interrupt) ? • 通常被定義為一種事件,可以改變處理器執行指令的順序。 • 為什麼要使用中斷? • 通知CPU事件發生好執行相對應的動作。

中斷(Interrupt) 現代電腦硬體結構

中斷(Interrupt) • 輪詢(Polling) • CPU需隨時監看其他週邊 • 中斷(Interrupt) • 其他週邊告知CPU已完成工作

中斷(Interrupt) • 輪詢(Polling) • 主單元輪流詢問從屬單元的狀態

中斷(Interrupt) • 中斷(Interrupt) • 某程式或週邊引起CPU注意,使CPU停止目前工作,執行相對應的動作 作業系統處理中斷步驟

中斷(Interrupt) • 中斷種類 • 硬體中斷 • 內部中斷(例外exception) • 外部中斷 • 軟體中斷

中斷(Interrupt) • 硬體中斷 • 內部中斷 (例外exception) • 因為錯誤或不合法所造成的中斷,例如:堆疊溢位(Stack Overflow)、除以零(Divided by Zero)、違反保護(Protect Volation)、除錯(Debug)

中斷(Interrupt) • 外部中斷 • 不可遮罩式(non-maskable interrupt) • Reset、WDT、Partity、Hard system error • 可遮罩式(maskable interrupt) • IRQ

中斷(Interrupt) • 軟體中斷 • 系統呼叫即是軟體中斷,又稱「監督者呼叫」(Supervitor Call,SVC)

中斷(Interrupt) • 陷阱(Trap) • 軟體產生的中斷;除以零、違法使用記憶體…等軟體產生的錯誤均稱「陷阱」

中斷(Interrupt) • 優先權(Priority) • NMI > MI > SI • 中斷向量表(IVT) • 每個中斷事件,配上相對應之處理的起始位址

中斷(Interrupt) • .LCvectors: • .align 4 /* offset 0: Reset and NMI */ • la $p0, HandleReset • jr $p0 • .align 4 /* offset 1: TLB fill */ • la $p0, HandleUndef • jr $p0 • .align 4 /* offset 2: PTE not present */ • la $p0, HandleUndef • jr $p0……略 NDSvectors

An Interruption is a control flow change of normal instruction execution generated by an Interrupt or an Exception. • When an interruption happens, • The processor stops processing current flow of instructions, • saves enough states for later resuming of the interrupted current flow, • disable interrupts, • enters SuperUser Mode, • starts executing a software interruption handler.

An interrupt is a control flow change event generated by an asynchronous internal or external source. It includes Hardware and Software Interrupts. • Hardware interrupt is any interrupt event generated from external agents or AndesCore™. • Software interrupt is an interrupt event generated by an instruction executing in the AndesCore™.

An exception is a control flow change event generated as a by-product of instruction execution. • For example, if an instruction with invalid format is encountered by an Andes processor core, a Reserved Instruction exception will be generated. • An exception can also be classified as precise, next-precise, and imprecise.

A precise exception • if when the exception handler is entered the instruction that causes the exception has not been completed. • Reserved Instruction • exception • A next-precise exception • if when the exception handler is entered the instruction that causes the exception has been completed but the next instruction has not been completed. • a data watchpoint exception

A imprecise exception • if when the exception handler is entered the instruction that causes the exception has been completed in the processor pipeline but the exact instruction complete/incomplete boundary following that instruction is unpredictable. • a Bus Error exception caused by a prefetch instruction

Interruption Handling in Hardware • interruption is handled in hardware based on the “interruption stack level transition” (ISLT). • Currently, four interruption stack levels are defined in the architecture, 0-3. • interruption stack level 0 means no interruption. • Hardware behaviors for handling an interruption are defined for three interruption stack level transitions, 0/1, 1/2, and 2/3.

Types of Interruptions • Reset/NMI • Cold Reset • Warm Reset • Non-Maskable Interrupt (NMI) • Interrupt • External interrupt • Performance counter interrupt • Software interrupt • Debug exception • Instruction breakpoint • Data address & value break • BREAK exception

TLB fill exception (Instruction/Data) • PTE not present exception (Instruction/Data) • Non-Leaf PTE not present • Leaf PTE not present • TLB miscellaneous exception • Read protection violation (Data) • Write protection violation (Data) • Page modified (Data) • Non-executable page (Instruction) • Access bit (Instruction/Data) • Reserved PTE Attribute (Instruction/Data) • TLB VLPT miss (Instruction/Data) • System Call exception

General exception • Trap exception • Arithmetic exception • Reserved instruction exception • Reserved value exception • Privileged instruction exception • Alignment check exception (Instruction/Data) • Precise bus error (Instruction/Data) • Imprecise bus error (Instruction/Data) • Nonexistence local memory address (Instruction/Data) • MPZIU control (Instruction/Data) • Coprocessor N not-usable exception • Coprocessor N-related exception

Machine error exception (Instruction/Data) • Cache locking error • TLB locking error • TLB multiple hit • Cache parity/ECC error • unimplemented page size error • Illegal parallel memory accesses (Audio extension)

Interruption Vectored Entry Point • Interruption Vectored Entry Points are defined for two different modes. • Internal Vectored Interrupt Controller (IVIC) mode • interrupts are prioritized inside an AndesCore™ using the internal interrupt controller logic. • External Vectored Interrupt Controller (EVIC) mode • interrupts are prioritized outside AndesCore™ using an external interrupt controller.

The starting address of the vectored offset table can be programmed using the “Interruption Vector Base” (IVB) system register. • The starting base address is 64KB-aligned. • The size of the vectored entry point can be configured using “ESZ” field of the IVB system register from 4 bytes to 16/64/256 bytes.

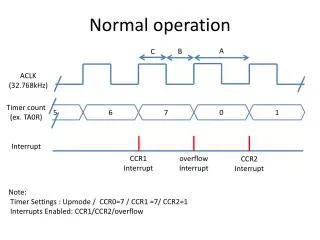

Entry Points for Internal VIC Mode • 16 entry points (9 exception + 7 interrupt) • 4 bits offset

Entry Points for External VIC Mode • 73 entry points (9 exception + 64 interrupt) • 7 bits offset Offset Entry point 0 Reset/NMI 1 TLB fill 2 PTE not present 3 TLB misc 4 TLB VLPT miss 5 Machine Error 6 Debug related 7 General exception 8 Syscall 9-72 VEP 0-63

參考資料 • http://vrschool.ice.cycu.edu.tw/vrschool/Course/OS/%E6%8A%95%E5%BD%B1%E7%89%87/%E4%BD%9C%E6%A5%AD%E7%B3%BB%E7%B5%B1%E7%AC%AC%E4%BA%8C%E7%AB%A0/sld002.htm • http://tw.myblog.yahoo.com/embedded_system_book/article?mid=20 • http://cs101.cs.ccu.edu.tw/index.php/Top_half#.E4.B8.AD.E6.96.B7.E6.8F.8F.E8.BF.B0.E5.99.A8.E8.A1.A8.E6.A0.BC