Server Switch

Server Switch. Carly Ho Sarah Alsulaiman. Programmability?. Commodity chips have limited programmability, not comparable to even general purpose CPUs FPGA:

Server Switch

E N D

Presentation Transcript

Server Switch Carly HoSarah Alsulaiman

Programmability? • Commodity chips have limited programmability, not comparable to even general purpose CPUs • FPGA: • C to HDL (SystemC ), combine HLL with concurrency models to allow faster design cycles. (Cadence, Synopsys and Agility Design Solutions) • Flow to HDL, a graphical dataflow approach to high-level design entry. (Annapolis Micro Systems, Inc.'s CoreFire Design Suite and National Instruments LabVIEW)

Best Programmable Device? • Microcontroller • Electronics Technology magazine awarded Stratix IV GX FPGA “Award for the best programmable device”

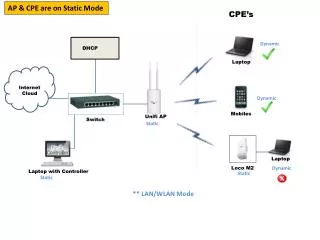

Tradeoffs • Processing traffic: • Driver: higher performance, more effort to program and debug • User space: easy for development but sacrifice performance • Two step indirect lookup key extraction • Between extra ASIC logic and TCAM space

Evaluation Issues • Most of the tests only compare one other system setup • The BCube network architecture they used was also built by many of the same paper writers—would it perform differently on different server architecture?

Problems • In-network caching: • increases CPU usage but saves bandwidth • Cost of 14% CPU usage even when cache hit ratio = 0 • Extra delay to generate a QNC queue reply messages • User library based on Broadcom SDK, only on Linux and VxWorks • PCI-E latency • Field matching is limited by the HW

Limitations • Limited hardware forwarding programmability • High packet processing latency due to switching chip to CPU communications • Restricted form factor and low speed • The internal bandwidth doesn’t match the total external one. Because they don’t think all traffic to be delivered to CPU