Virtual Memory

Virtual Memory. From course notes 0657.201 University of Waikato. Some material by Tony McGregor tonym@cs.waikato.ac.nz Other material from: The Architecture of Computer Hardware and Systems Software: An Information Technology Approach Irv Englander, John Wiley and Sons (WIE)

Virtual Memory

E N D

Presentation Transcript

Virtual Memory From course notes 0657.201 University of Waikato. Some material by Tony McGregor tonym@cs.waikato.ac.nz Other material from: The Architecture of Computer Hardware and Systems Software: An Information Technology Approach Irv Englander, John Wiley and Sons (WIE) ISBN: 0471310379 and Operating System Concepts, Peterson and Silberschatz, Addison Wesley, ISBN 0-201-06097-3. Chapter 5. also Drawings and notes by me Richard Jones – richard@ib-computing.com

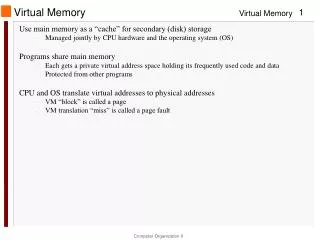

Virtual (logical) Memory • The user program sees memory as contiguous. • The actual program is spread throughout physical memory. • Hardware translates logical address references to physical addresses – effectively “relocating” code dynamically.

Paging • The logical address space is divided into relatively small, fixed size pages. • Physical memory is divided into the same sized units (frames). • Hardware translates pages to frames. virtual address space of process 1 address translation virtual address space of process 2 physical memory

Pages and frames see, Peterson and Silberschatz, p160 and Englander, p540 page 0 page 1 page 2 page 3 logical memory page table frame number physical memory page/frame sizes are determined by the hardware.

Page number and offset The MMU splits (logical) addresses into a page number and an offset within the page.

Page table physical memory page offset 3D 7A1 2F357 7A1 Englander p 540 page table

Features of paging • Logical and physical addresses do not have to be the same size. • There is no external fragmentation – any free memory frame can be allocated to a process. • Internal fragmentation still occurs if a program does not end exactly on a page boundary.

Virtual vs Physical Memory base base

Disadvantage of paging • Since the logical address must be converted to a physical address using table lookup, access to memory is slowed by a factor of 2. • Various schemes are incorporated in the hardware to speed access – eg use of high-speed cache to store recently “hit” pages.

Where are they? page offset 3D 7A1 2F357 7A1 In this example, it is apparent that some pages are not in the page table. Where are they? What do we need to do if this happens?

Swap files • Primary memory is limited in size. • Pages can be held on secondary memory. • If the CPU tries to execute an instruction or use data on a page that is not in the page table a page fault (interrupt) is generated.

Page fault no page found page 3D located and loaded in instruction executed page table possibly an existing page is removed and stored page table updated

Page swapping • Most programs only access a small percentage of their memory space during any particular time of their execution. • The associated pages can be identified as a working set. • Some systems dynamically adjust the size of the working set by tracking page faults for each process.

Thrashing • Pages are regularly being swapped in and out as processes execute. This is slow compared to CPU clock time. • Sometimes pages of one process are replaced by another. • As the CPU switches between processes it can generate a huge number of page faults slowing the system dramatically.

Thrashing memory frames process A process B swap disk address translation process D process C switch to process B, not many pages in memory, load them in. switch to process C

Segmentation • Segments are larger units of memory than pages – represent another approach. • They are normally constructed by the compiler/assembler. • They can be swapped as a unit if thrashing occurs. • Segments can be tagged, indicating the type of data held.

Segments physical memory Operating System Concepts, Peterson and Silberschatz, Addison Wesley, isbn 0-201-06097-3, p160 1400 2400 3200 4300 4700 5700 6300 6700 segment 0 subroutine xyz stack function sqrt segment 3 symbol table segment 2 main program segment 4 logical address space segment 1

Segments • Segments can be a unit of memory protection – causing segmentation faults. • Segments (like code/.text) can be marked as read-only. • Segments can be shared among processes.

Unix executables tagged as read only (could be shared) .text copied into their own segments .data (initialised) .bss space is allocated Symbol table stack segment (un- initialised) Relocation table

Paged segmentation • Combination of segmentation and paging. • Segment table can be extended to include ownership and access bits. • Shared segments will have segment tables (in each shared process) which point to the same page table, access bits might be different.

Paged segmentation physical memory segment offset page offset Physical address 2F377 A1 3D 7A1 7 A1 Segment table - pointer to page table (1 segment table per process) Page table 4A - pointer to base physical address (1 page table per segment)

compiler compiler source code source code Paged segmentation physical memory In this scheme, as with ordinary segmentation, a .text (or code) segment can be shared between different processes. Each process has different data tables. segment table A page tables A process A page tables B segment table B process B

Segmented paging • Alternative scheme (not common). • Segment table with fixed number of entries. • Each entry points to the base of a page table. • Page table entry plus offset in logical address gives memory location.

Segmented paging physical memory offset in page table page offset Physical address 3 2F377 A1 73 A1 Segment table - pointer to base in page table (part of) Page table

Conclusion • Memory management systems are constrained by the hardware. • Logical addresses mapped to physical addresses – inefficient to do in software. • Any of the schemes can include swapping to cater for more jobs than physical memory permits.