Exploring Digital Logic through NAND and D Flip-Flop Circuits

DESCRIPTION

This experiment, led by teacher Wu Shao-Hsun with assistants Jiang Chang-Ting and Zheng Chong-Jie, focuses on digital logic circuit design using NAND gates and D flip-flops. The equipment includes two 7400 NAND ICs, one LED, one D flip-flop, and additional components for wiring. The experiment aims to construct and analyze circuits that illustrate the behavior of positive edge-triggered D flip-flops. Students will gain hands-on experience in building, testing, and understanding the dynamics of sequential logic circuits.

1 / 4

Download Presentation

Exploring Digital Logic through NAND and D Flip-Flop Circuits

An Image/Link below is provided (as is) to download presentation

Download Policy: Content on the Website is provided to you AS IS for your information and personal use and may not be sold / licensed / shared on other websites without getting consent from its author.

Content is provided to you AS IS for your information and personal use only.

Download presentation by click this link.

While downloading, if for some reason you are not able to download a presentation, the publisher may have deleted the file from their server.

During download, if you can't get a presentation, the file might be deleted by the publisher.

E N D

Presentation Transcript

Logic Experiment 8 老師:伍紹勳 助教:江長庭 鄭仲傑

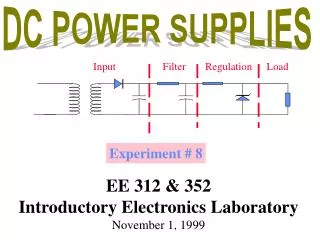

Equipment IC: 7400 (NAND) x 2、LED x 1

1 S’ 2 5 Q Clock 6 Q’ 3 R’ 4 D Edge-triggered Flip-flop :D-type positive edge triggered FF :

More Related