10 さあ! ロジックIC の勉強がはじまるよ!

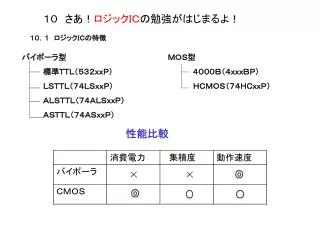

10 さあ! ロジックIC の勉強がはじまるよ!. 10.1 ロジックICの特徴. バイポーラ型 MOS型 標準TTL(532xxP) 4000B(4xxxBP) LSTTL(74LSxxP) HCMOS(74HCxxP) ALSTTL(74ALSxxP) ASTTL(74ASxxP) . 性能比較. 10.2 入出力特性とスレショルドレベルについて. 10.3 HCMOSの入出力電圧と論理レベル.

10 さあ! ロジックIC の勉強がはじまるよ!

E N D

Presentation Transcript

10 さあ!ロジックICの勉強がはじまるよ!10 さあ!ロジックICの勉強がはじまるよ! 10.1 ロジックICの特徴 バイポーラ型 MOS型 標準TTL(532xxP) 4000B(4xxxBP) LSTTL(74LSxxP) HCMOS(74HCxxP) ALSTTL(74ALSxxP) ASTTL(74ASxxP) 性能比較

10.2 入出力特性とスレショルドレベルについて10.2 入出力特性とスレショルドレベルについて

10.3 HCMOSの入出力電圧と論理レベル10.3 HCMOSの入出力電圧と論理レベル

10.4 LSTTLの入出力電圧と論理レベル10.4 LSTTLの入出力電圧と論理レベル

10.6 伝播時間(プロバゲーションタイム)10.6 伝播時間(プロバゲーションタイム)

10.8 NOT回路または、インバータ ( 74LS04 )10.8 NOT回路または、インバータ ( 74LS04 ) NOT回路1個の回路図

10.10 NAND,NOR回路 (74LS00 74LS02)10.10 NAND,NOR回路 (74LS00 74LS02)

10.11 ゲートのシンボル変換 アクテイブな信号を明確にして回路を書く10.11 ゲートのシンボル変換 アクテイブな信号を明確にして回路を書く

10.12 ゲート回路のいろいろ! 1.半加算器(Half adder) さあ!シミュレーションしよう(Digiral Mode )

3.フリップフロップ さあ、上の回路をシミュレーションしてみよう!

11.1 シュミットトリガIC 緩やかに変化する信号入力には、このICで受ける 三角波の設定 ①TTL ICをテストする スレショルドレベルのON点OFF点とその幅を確認しよう!

②CMOS ICでのテスト TTLとCMOSのスレショルドレベルの違いについて、理解する。このICは、シュミットつきであるが、シュミットの無いICでも同様のテストするとスレショルドレベルがはっきりするが、下の波形では、3.45-1.55/2+1.55=2.5vとなり理論的には、Vccの1/2となる。

③では、シュミットICが無い場合、普通のNotで実現しよう!③では、シュミットICが無い場合、普通のNotで実現しよう!

11.3 発振回路2 初期値設定=0

11.5 D/Aコンバータ 8ビットのD/Aコンバータです。こんなに簡単にできちゃうんですね! シミュレーションで確かめよう。

11.6 3ステートゲート(トライステート)11.6 3ステートゲート(トライステート) 問題: SELの信号がLレベルの時、AとYがつながり、Hレベルの時BとYがつながる回路を下に書きなさい。

第11回での補足・電磁コイル電流の遮断について第11回での補足・電磁コイル電流の遮断について

半波整流では、断続波になり電磁コイルが振動する半波整流では、断続波になり電磁コイルが振動する

D2のダイオードをいれるとL1に蓄えられ電磁エネルーギがD2ダイオードを通して回生しコイルが保持される。D2のダイオードをいれるとL1に蓄えられ電磁エネルーギがD2ダイオードを通して回生しコイルが保持される。

電源投入後、150ms後にQ1のスイッチをOffすると高圧パルス電圧が発生する電源投入後、150ms後にQ1のスイッチをOffすると高圧パルス電圧が発生する シミュレーションの際、このFETの耐圧データを1200Vに変更した。 Q1のFETスイッチ Onから Offに変る点

CR型サージアブソーバを挿入した場合C1=1uF R2=180ΩCR型サージアブソーバを挿入した場合C1=1uF R2=180Ω

C1=10uF、R2=22Ωにすると R2に流れる電流 このコンデンサーC1が大きいと、Q1の接点開放時も電流が流れるので注意!

コイルに流れる電流の切るタイミングでサージの出方が変るコイルに流れる電流の切るタイミングでサージの出方が変る

電流のピークでR2の電流を見るとR2の消費電力は?電流のピークでR2の電流を見るとR2の消費電力は?

ジュール熱 自己誘導のために周りの媒質中に蓄えられるエネルギー 回路に生ずる過渡電流によるジュール熱は、初めに蓄えられた電磁エネルギーに等しいよって電磁エネルギ は、起電力を取り去った抵抗Rで消費される

Dラッチが8個入って1個のICになっている。Dラッチが8個入って1個のICになっている。 74LS373の内部構成

JKフリップフロップ(74LS112)で8ビットシフトレジスタを作ろう!JKフリップフロップ(74LS112)で8ビットシフトレジスタを作ろう!

13.2 4bit デジタルコンパレータ(4-BIT MAGNITUDE COMPARATOR)

13.4 カウンタIC 10進カウンタ (74LS160)13.4 カウンタIC 10進カウンタ (74LS160)

13.7 7セグメント・デコーダ・ドライバー13.7 7セグメント・デコーダ・ドライバー

13.8 BCD 2桁プリセットカウンタ回路13.8 BCD 2桁プリセットカウンタ回路