KT-M128 Peripheral Device

KT-M128 Peripheral Device. Seven-Segment Timer / Counter0 2010. 7. 30 조 승훈. Reference: AVR ATmega128 정복 , ohm 사 IAR EWAVR 컴파일러를 이용한 AVR ATmega128 마이크로 컨트롤러 , 성안당 ATmega128 Register_ver0.9, 단국대 Electron 조상민 NewTC 강의 자료 (I/O PORT, Timer/Counter, Interrupt), http://NewTC.co.kr.

KT-M128 Peripheral Device

E N D

Presentation Transcript

KT-M128 Peripheral Device Seven-Segment Timer / Counter0 2010. 7. 30 조 승훈 Reference: AVR ATmega128 정복, ohm사 IAR EWAVR 컴파일러를 이용한 AVR ATmega128 마이크로 컨트롤러, 성안당 ATmega128 Register_ver0.9, 단국대 Electron 조상민 NewTC 강의 자료 (I/O PORT, Timer/Counter, Interrupt), http://NewTC.co.kr

Index • Seven-Segment • Timer / Counter0 • AVR Interrupt • Source Code

Seven-Segment • Overview • 7개의 막대형 LED를 사용하여 아라비아 숫자나 간단한 기호 또는 몇 가지의 영문자를 표시 할 수 있도록 만든 LED 복합 소자 • FND (Flexible Numerical Display) 라 부름 • 대부분의 7-Segment는 추가로 dot point를 추가하여 1바이트 디지털 데이터를 사용하여 1글자를 디스플레이 하는데 적합 • 74LS47 (BCD-to-7-Segment Decoder / Driver)를 사용하면 4비트의 병렬 데이터로 1글자를 보다 쉽게 디스플레이 할 수 있음 • 공통 애노드형, 공통 캐소드형이 있음 • Static Display 구동 방식, Dynamic Display 구동 방식이 있음

Seven-Segment • 7Segment의 구조 • Common Anode형과 Common Cathode형으로 나뉨 • 어느 방식을 사용할지는 7Segment LED를 제어하는 회로의 출력 단 데이터 논리상태나 각 Segment를 점등하기 위한 Switching 소자의 종류에 따라 결정 • Common Cathode형 • 제어회로 출력 단의 논리상태가 L일 때 제어하기 편함 • Common Anode형 • 제어회로 출력 단의 논리상태가 H일 때 제어하기 편함

Seven-Segment • 7Segment의 구동 방식 • Static Display • 각 7Segment 별로 전용 Latch 사용 • 장점: 소프트웨어적으로 처리가 간편 상대적으로 CPU의 부담이 적음 • 단점: 항상 켜져 있으므로 전력 소모가 큼 표시 자리가 늘어나면 하드웨어적으로 복잡해짐 • Dynamic Display • 한번에 한 개의 7Segment를 구동하되, 착시현상을 이용하여 순차적으로 Enable을 인가 • 장점: 상대적으로 전력 소모가 적음 구동해야 할 7Segment가 많을 때 유리 • 단점: 상대적으로 CPU의 부담이 큼

Seven-Segment • KT-M128 7Segment 회로도 한 7Segment의 LED 컨트롤 (Data) 7-Segment의 Digit 컨트롤

Seven-Segment • KT-M128의 7Segment 메모리 주소 • Seven-Segment Data 출력 메모리 번지: 0x8002 (Write 전용) • Seven-Segment Digit 출력 메모리 번지: 0x8003 (Write 전용) Data[7] Seven-Segment – A Segment Data[6] Seven-Segment – B Segment Data[5] Seven-Segment – C Segment Data[4] Seven-Segment – D Segment Data[3] Seven-Segment – E Segment Data[2] Seven-Segment – F Segment Data[1] Seven-Segment – G Segment Data[0] Seven-Segment – Dot Point Segment Digit[n] n번째 자리 수 Enable(H: Disable, L: Enable)

AVR Timer /Counter • Timer / Counter Overview • 입력으로 들어오는 펄스를 셈하는 장치 • 입력으로 들어오는 펄스가 어디에 존재하느냐에 따라 Timer와 Counter로 나눔 • AVR ATmega128에는 범용 타이머 / 카운터가 4개 존재 • Timer/Counter0 (8bit) • Timer/Counter1 (16bit) • Timer/Counter2 (8bit) • Timer/Counter3 (16bit)

AVR Timer /Counter • Timer와 Counter의 차이점 • Timer • 내부 Clock(빠름 / 분주 가능: 범위 내에서 Clock 선택 가능) – 동기모드 • 타이머는 MCU의 내부 Clock(Clk I/O > 분주기 > ClkT)을 이용 • 일정시간 간격의 펄스를 만들어 내거나, 일정시간 경과 후에 인터럽트 발생 가능 • Counter • 외부 Clock (느림 / 분주 불가능: 외부 Clock 그대로 사용) – 비 동기모드 • Counter는 외부 핀 (TOSC1, TOSC2, T1, T2, T3)을 통해 들어오는 펄스를 계수 (Edge Detector)하여 Event Counter로서 동작 (Pulse = Event, Counter = Number of Event) • Timer / Counter Register • Timer / Counter Control Register (TCCRn) • Timer / Counter Register (TCNTn) • Output Compare Register (OCRn) • Interrupt • Timer / Counter Interrupt Flag Register (TIFR) • Timer / Counter Interrupt Mask Register (TIMSK)

AVR Timer /Counter • 8Bit Timer / Counter 0 • Timer / Counter0의 특징 • 싱글 채널 카운터 • Clear Timer on Compare Match 기능 (Auto Reload 기능) • 글리치가 없는 Phase Correct PWM 기능 • 주파수 발생 기능 • 10bit 프리스케일러 기능 • Timer0 Overflow Interrupt와 Timer0 Compare Match Interrupt • I/O Clock과는 별도로 32.768kHz를 인가 가능한 핀 (TOSC1, TOSC2 핀)

AVR Timer /Counter • BOTTOM : ox00일 경우 카운터가 Bottom에 도달 • MAX : 0xFF일 경우 카운터가 MAX에 도달 • TOP : Max or OCR0 값에 도달

AVR Timer /Counter • 프리스케일러 (PreScaler) • 전치 분주기 • 총 8개의 스케일을 가지고 있음 • 분주비가 1:8일 경우, 시스템 Clock이 8번 들어 올 때, 프리스케일러를 통과한 Clock은 1번의 Clock이 발생 Prescaler for Timer / Counter0 Prescaler for Timer / Counter0 (ASSR[3]) (SFIOR[1]) (TCCR0[2:0])

AVR Timer /Counter • Timer / Counter 관련 레지스터 (I/O Reg 영역에 Mapping) • SFIOR (Special Function I/O Register) • Bit 7 : TSM (Timer / Counter Synchronization Mode) • 1: Timer / Counter0의 동기 모드, PSR0와 PSR321에 쓴 값은 유지 됨 • 0: PSR0와 PSR321에 쓴 값은 하드웨어에 의해 클리어 됨 • Bit 1 : PSR0 (Prescaler Reset Timer / Counter0) • 1: Timer / Counter0의 Prescaler를 리셋 • 0: 영향 없음

AVR Timer /Counter • ASSR (Asynchronous Status Register) • Bit 3 : AS0 (Asynchronous Timer / Counter0) • 0: Clock 소스 = ClkI/O (동기 모드) • 1: Clock 소스 = TOSC1 (비동기 모드) • Bit 2 : TCN0UB (Timer /Counter (TCNT0) Update Busy) • 비동기 모드일 때 TCNT0에 새로운 값이 라이트되면 셋 • Bit 1 : OCR0UB (Output Compare Register (OCR0) Update Busy) • 비동기 모드일 때 OCR0에 새로운 값이 라이트되면 셋 • Bit 0 : TCR0UB (Control Register (TCCR0) Update Busy) • 비동기 모드일 때 TCCR0에 새로운 값이 라이트되면 셋

AVR Timer /Counter • TCCR0 (Timer /Count0 Control Register) • Bit 7 : FOC0 (Force Output Compare) • 1: 강제로 OC0 단자에 출력 비교가 매치된 신호 출력 (PWM 아닌 경우에 유효) • Bit 6 : WGM00 (Waveform Generation Mode) • Counter의 카운팅 방향, MAX(TOP) 카운터 값의 소스 및 Mode 선택 • Bit 5 – 4 : Com01 - Com00 (Compare Match Output Mode) • OC0 핀 기능 설정 • Bit 3 : WGM01 (Waveform Generation Mode) • Counter의 카운팅 방향, MAX(TOP) 카운터 값의 소스 및 Mode 선택 • Bit 2 – 0 : CS02 – CS00 (Clock Select) • Clock의 분주 비율 설정

AVR Timer /Counter Waveform Generation Mode Compare Output Mode, non PWM Mode

AVR Timer /Counter • TCNT0 (Timer / Counter0 Register) • Timer / Counter0의 8bit 카운터 값을 저장하고 있는 레지스터

AVR Timer /Counter • OCR0 (Timer / Counter0 Output Control Register) • TCNT0 값과 비교하여 OC0 핀에 출력신호를 발생하기 위한 8bit값을 저장하는 레지스터

AVR Timer /Counter • TIMSK (Timer / Counter Interrupt Mask Register) • Timer / Countern에서 발생하는 Interrupt의 개별적으로 enable • Bit 1: OCIE0 (Timer / Counter0 Output Compare Match Interrupt Enable) • OCIE0 bit가 1로 설정되고 SREG의 I비트가 1로 설정되어 있으면 Timer / Counter0의 출력 비교 Interrupt가 enable • 이 때, Timer / Counter0 출력비교 Interrupt가 발생하면 TIFR의 OCF0 bit가 1이 되면 이 Interrupt가 처리 됨 • Bit 0: TOIE0 (Timer /Counter0 Overflow Interrupt Enable) • TOIE0 bit와 I bit가 1로 설정되어 있으면 Overflow Interrupt가 enable 됨 • 이 때, TIFR의 TOV0 비트가 1이 되면 ISR이 실행 됨

AVR Timer /Counter • TIFR (Timer / Counter Interrupt Flag Register) • Timer / Counter에서 발생하는 Interrupt Flag를 저장 • Bit 1: OCF0 (Timer / Counter0 Output Compare Flag) • TCNT0과 OCR0의 값을 비교, 같으면 이 bit가 1로 설정되고, 출력비교 Interrupt가 발생, 이 Interrupt가 처리되면 자동으로 0으로 Clear 됨 • Bit 0: TOV0 (Timer / Counter0 Overflow Flag) • Timer / Counter0에서 Overflow가 발생하면 자동으로 1로 설정 됨 • 이 bit가 1이 되면 Overflow Interrupt 발생 • Interrupt가 처리되면 자동으로 0으로 Clear 됨 • Phase PWM Mode에서는 Timer / Counter0이 0x00에서 카운트 방향을 바꿀 때 1로 설정 됨

AVR Timer /Counter • Timer • 각 타이머에서 사용하는 Clock에 대한 설정필요 • 프리스케일러(PreScaler) 값으로 조절 가능 • 프리스케일러 값은 각 타이머의 컨트롤 레지스터(TCCRn)에서 설정 • 각 타이머 레지스터 (TCNTn)에 얼마마다 한번 씩 인터럽트를 걸게 할 것인지와 관련된 값을 써주면 됨 • 타이머 인터럽트 관련 레지스터들을 설정 필요 • 타이머 인터럽트에서는 TIMSK 레지스터만 설정

AVR Timer /Counter • Timer / Counter0의 Output Compare 장치 • 8bit 비교기 : 연속해서 TCN0 값과 OCR0 값을 비교 • TCNT0 값과 OCR0 값이 같을 때마다 match 신호 발생 • match 신호는 Timer Clock의 다음 Cycle에서 OCF0 (Output Compare Flag) 를 셋 • OCIE0 bit와 SREG 레지스터의 I bit가 1로 Set되어 있으면 OCF0는 Output Compare Interrupt 발생 시킴 • OCF0 Flag는 Interrupt가 실행되고 나서 자동으로 Clear 됨 (OCF0 bit에 1을 써서 Software적으로 Clear해도 됨)

AVR Timer /Counter • Timer / Count0 관련 레지스터 • TCCR0 (Timer / Counter Control Register) • Bit 7 : FOC0 (Force Output Compare) • 1: 강제로 OC0 단자에 출력 비교가 매치된 신호 출력 (PWM이 아닌 경우 유효) • Bit 6 : WGM00 (Waveform Generation Mode)

AVR Timer /Counter • Timer / Counter0의 동작 모드 • WGM[1:0] (Waveform Generation Mode, TCCR0 Reg)와 COM[1:0] (Compare Output Mode, TCCR0 Reg)에서 설정 • WGM : 카운터의 순서에 영향을 비침 • COM : PWM 모드에서 (Non)inverting mode를 결정 Non-PWM 모드에서 compare match 시점에서 출력이 1로 Set되는지, 0으로 Clear 되는지, Toggle인지를 결정 • 4가지 동작 모드 지원 • Normal Mode • CTC (Clear Timer on Compare Match) Mode • Fast PWM Mode • Phase Correct PWM Mode

AVR Timer /Counter • Normal Mode (WGM[1:0] = 0으로 설정) • 동작 모드 중 가장 간단한 모드 • 항상 상향 카운터 • 카운트 도중 Clear되지 않음 • TOP이 oxFF가 되면 다시 BOTTOM(0x00)에서 시작 (Overflow) • TOV0 (Timer /Counter Overflow Flag)는 TCNT0 값이 0이 되는 시점에서 1로 Set 됨 • 비교매치(Compare Match) 인터럽트 발생 • 파형을 예상하지 못하기 때문에 비 추천

AVR Timer /Counter • CTC Mode (Compare Timer on Compare Match Mode) • WGM[1:0] = 2로 설정 • 주파수 분주 기능으로 주로 사용 (PortB4 = OC0) • DDR 레지스터 값을 출력으로, COM[1:0]을 1로 설정 • 항상 상향 카운터 • 0x00 ~ OCR0 계수 동작 반복 • OCR0값과 TCNT0 값이 같으면 카운트 도중 Clear • MAX이거나 OCR0 값일 때, Overflow Interrupt 발생 • COMP 인터럽트와 동일하게 작동되기 때문에 비 추천

AVR Timer /Counter • FAST PWM • 높은 주파수 PWM 파형발생이 필요할 때 사용 • 상향 카운터 (Single-Slope Operation) • 0x00 ~ 0xFF 계수 동작 반복 • TCNT0과 OCR0의 Compare Match되면 OC0에 LOW 출력 (COM0[1:0] = 2) • oxFF -> 0x00 Overflow되면 OC0에 HIGH 출력 (COM[1:0] = 2)

AVR Timer /Counter • Phase Correct PWM • 높은 분해능의 PWM출력 파형을 발생하는데 사용 • 상향카운터 0x00 -> 0xFF • 하향카운터 0xFF -> ox00 • 0x00 ~ oxFF ~ ox00 계수 동작 반복 • 상향카운터 비교매치>> OC0 = 0 출력 (COM0 1 : 0 = 2) • 하향카운터 비교매치>> OC0 = 1 출력 (COM0 1 : 0 = 2)

AVR Timer /Counter • Match 된 다음 Cycle에 Set • OCIE0 bit와 SREG의 I 비트가 1이면 Output Compare Interrupt 발생 • Interrupt가 실행되고 나면 OCF는 자동으로 Clear 동작 모드 비트 Compare Output Mode

AVR Timer /Counter CS00~ CS02 AS0 • 모드의 동작에 따라 ClkTn에서 • 카운터가 클리어, 증가, 감소 • AS0를 이용하여 외부 또는 내부 Clock 소스 설정 • CS[2:0]를 설정하여 사용 주파수로 분주 가능 • TCCR0 레지스터의 TGM01~00으로 모드 설정 • TCNT0과 OCR0는 8bit로 구성 • BOTTOM : ox00일 경우 카운터가 Bottom에 도달 • MAX : 0xFF일 경우 카운터가 MAX에 도달 • TOP : Max or OCR0 값에 도달

Timer / Counter • Timer / Counter 0과 2 • 공통점 • 8bit 구조 • Overflow • PWM과유사한 기능 • 제어방식 • 차이점 • Timer / Counter0은 32.768KHz의 크리스탈을 접속하는 TOSC1 및 TOSC2 단자를 가짐 • RTC 기능을 갖도록 할 수 있음 • 다른 Timer / Counter와는 다르게 내부 클럭을 사용하든 외부 클럭을 사용하든 모두 프리스케일러의 분주 기능 사용가능

AVR Timer /Counter • Timer / Counter Summary

AVR Interrupt • Interrupt Overview • CPU가 현재 처리하고 있는 일보다 급하게 처리해야 할 사건이 발생 했을 때, 현재 수행중인 일을 잠시 중단하고 급한 일을 처리한 후 본래의 일을 다시 수행하는 것 • 프로그램 된 순서대로 일을 처리하는 것이 아니라 발생 시기를 예측 할 수 없는 사건을 처리하는 데 효율적인 방법 • 인터럽트 처리 과정 • 인터럽트가 준비된 장치는 인터럽트 요구 플래그 bit를 세트하고 CPU에 인터럽트 요구 • CPU는 인터럽트 확인(INTA) 신호를 보내고, INTA를 받은 I/O장치는 인터럽트 요구 삭제 • CPU는 PC, PSW, 레지스터 등을 Stack에 저장 • CPU는 인터럽트 서비스 루틴(ISR)의 주소를 PC에 적재 • 인터럽트 서비스 루틴 수행 • PSW, 레지스터 등을 Stack으로부터 복귀 • 본래의 메인 프로그램으로 북귀

AVR Interrupt • Interrupt Vector Reset 및 Interrupt Vector의 위치 설정 BOOTRST in Fuse High Byte

AVR Interrupt • Interrupt 관련 Register • MCUCR (MUC Control Register) • Bit 1 : Interrupt Vector Select • Interrupt Vector 설정 • Bit 0 : Interrupt Vector Change Enable • 0: Interrupt Vector 바꿈 차단 • 1: Interrupt Vector 바꿈 허용

AVR Interrupt • EICRA (External Interrupt Control Register A) • Bit 7 – 6 (External Interrupt 3 Sense Control) • 외부 인터럽트 INT3의 트리거 방식 설정 • Bit 5 – 4 (External Interrupt 2 Sense Control) • 외부 인터럽트 INT2의 트리거 방식 설정 • Bit 3 – 2 (External Interrupt 1 Sense Control) • 외부 인터럽트 INT1의 트리거 방식 설정 • Bit 1 – 0 (External Interrupt 0 Sense Control) • 외부 인터럽트 INT0의 트리거 방식 설정

AVR Interrupt • EICRB (External Interrupt Control Register B) • Bit 7 – 6 (External Interrupt 7 Sense Control) • 외부 인터럽트 INT7의 트리거 방식 설정 • Bit 5 – 4 (External Interrupt 6 Sense Control) • 외부 인터럽트 INT6의 트리거 방식 설정 • Bit 3 – 2 (External Interrupt 5 Sense Control) • 외부 인터럽트 INT5의 트리거 방식 설정 • Bit 1 – 0 (External Interrupt 4 Sense Control) • 외부 인터럽트 INT4의 트리거 방식 설정

AVR Interrupt • EIMSK (External Interrupt Mask Register) • Bit 7 – 0 : External Interrupt Mask Register • 1: 각각의 인터럽트 허용 • 0: 각각의 인터럽트 금지

AVR Interrupt • EIFR (External Interrupt Flag Register) • Bit 7 – 0 : External Interrupt Flag Register • 각각의 인터럽트 발생

Source Code #include <avr/io.h> #include <avr/interrupt.h> #define EX_SS_DATA (*(volatile unsigned char *)0x8002) #define EX_SS_SEL (*(volatile unsigned char *)0x8003) void delay(int n); const char segment_data[10] = {63, 6,91,79,102,109,125,39,127,103}; unsigned char display_num[4]={0,0,0,0}; // Seven segment 4자리 숫자 출력 버퍼 void port_init(void) { PORTA = 0x00; DDRA = 0xff; //1출력 0입력 for 7segment PORTB = 0x00; DDRB = 0x00; PORTC = 0x00; //m103 output only DDRC = 0x0f; //Low 8bit output PORTD = 0x00; DDRD = 0x00; PORTE = 0x00; DDRE = 0x00; PORTF = 0x00; DDRF = 0x00; PORTG = 0x00; DDRG = 0x03; //lower 2bit output } //TIMER0 initialize - prescale:64 // WGM: Normal // desired value: 1KHz // actual value: 1.000KHz (0.0%) void timer0_init(void) { TCCR0 = 0x00; //stop ASSR = 0x00; //set async mode TCNT0 = 0x06; //set count OCR0 = 0xFA; TCCR0 = 0x04; //start timer } unsigned char digit_num=0; //#pragma interrupt_handler timer0_ovf_isr:17 ISR(TIMER0_OVF_vect) { TCNT0 = 0x06; //reload counter value digit_num++; digit_num = digit_num%4; EX_SS_SEL = 0x0f; EX_SS_DATA = segment_data[display_num[digit_num]]; EX_SS_SEL = ~(0x01 << digit_num); }

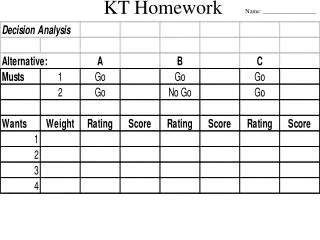

Source Code //call this routine to initialize all peripherals void init_devices(void) { //stop errant interrupts until set up asm("cli"); //disable all interrupts XDIV = 0x00; //xtal divider XMCRA = 0x00; //external memory port_init(); timer0_init(); MCUCR = 0x80; //enable int EICRA = 0x00; //ext ints control reg A EICRB = 0x00; //ext ints control reg B EIMSK = 0x00; //ext Int mask reg TIMSK = 0x01; //timer interrupt sources ETIMSK = 0x00; //extended timer interrupt sources asm("sei"); //re-enable interrupts //all peripherals are now initialized } int main(void) { int i=0; init_devices(); while(1){ i++; display_num[0] = (i%10000)/1000; display_num[1] = (i%1000)/100; display_num[2] = (i%100)/10; display_num[3] = (i%10); delay(1000); } } void delay(int n) { volatile int i,j; for(i=1;i<n;i++) { for(j=1;j<600;j++); } }