Arhitecturi tipice circuitelor programabile

130 likes | 282 Views

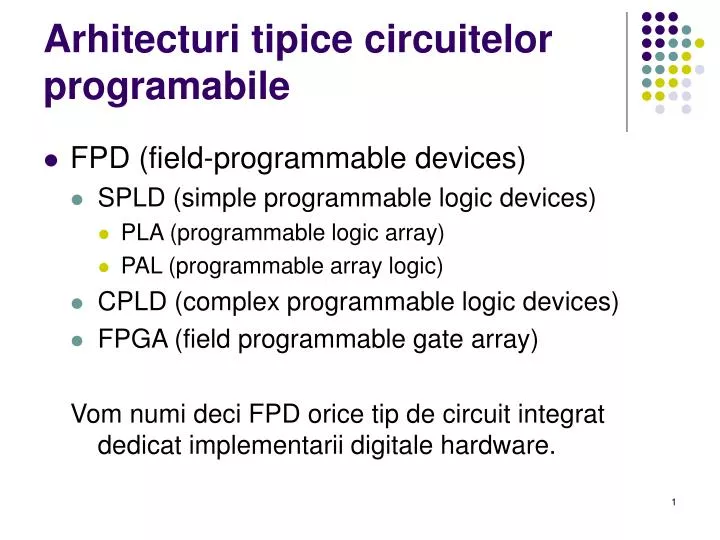

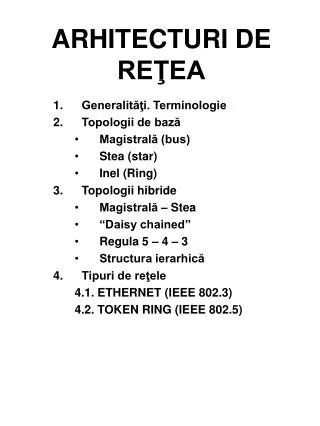

Arhitecturi tipice circuitelor programabile. FPD (field-programmable devices) SPLD (simple programmable logic devices) PLA (programmable logic array) PAL (programmable array logic) CPLD (complex programmable logic devices) FPGA (field programmable gate array)

Arhitecturi tipice circuitelor programabile

E N D

Presentation Transcript

Arhitecturi tipice circuitelor programabile • FPD (field-programmable devices) • SPLD (simple programmable logic devices) • PLA (programmable logic array) • PAL (programmable array logic) • CPLD (complex programmable logic devices) • FPGA (field programmable gate array) Vom numi deci FPD orice tip de circuit integrat dedicat implementarii digitale hardware.

A B C F0 F1 F2 F3 PLA • Este un FPD relativ mic care contine doua nivele de logica, un front SI si un front SAU, ambele programabile

PAL • Este un FPD relativ mic care contine doua nivele de logica, un front SI si un front SAU, primul fiind programabil, iar cel de-al doilea fix ( o anumita coloana de porti SAU are acces doar la un anumit set de termeni SI)

CPLD • Este un PLD complex care grupeaza intr-un singur chip mai multe blocuri de tip SPLD.

FPGA • Acestea sunt cele mai avansate elemente din familia de FPD, prezentand cea mai inalta capacitate logica. FPGA se diferentiaza de CPLD in primul rand prin resurse al caror numar de intrari este mai mic, permitand utilizarea mai eficienta a acestora.

FPGA • Arhitectura programabila de CLB ( Configurable Logic Blocks) • Perimetru de IOB ( Input/Output Blocks) grupat in bancuri dupa standardul electric utilizat • Multiple DLL ( Delay-Locked Loops) / DCM (Digital Clock Manager) corespunzatoare zonelor chipului • Coloane de BRAM (Block RAM) situate intre CLB si IOB

Efecte ale constrangerilor de implementare • Viteza circuitelor:

Efecte ale constrangerilor de implementare Inserarea bistabililor in lanturile de logica asigura o viteza de functionare mai mare, dar in acelasi timp produc si un delay de procesare mai ridicat. • Puterea disipata: depinde de numarul de tranzitii al semnalelor pe unitatea de timp • Aria ocupata: utilizarea resurselor depinde de complexitatea procesarii digitale. Arie mare => disponibilitate de resurse scazuta => rute lungi => viteza scazuta a sistemului

Efecte ale constrangerilor de implementare • Programarea FPD Fiecare etapa se realizeaza cu ajutorul unor programe specifice Etapa de configurare necesita hardware specific tipului de arhitectura in care este utilizat FPD

Efecte ale constrangerilor de implementare • Hazardul: Daca timpul de parcurgere al rutelor insumat cu timpii de comutare al elementelor de logica nu este mai mic decat perioada ceasului de sistem, elementele sincrone ale acestuia pot stoca valori tranzitorii ale semnalelor Evitarea acestor situatii se fece prin intermediul constrangerilor de timp impuse de utilizator in etapa de implementare