Precise Interrupts and Pipelines in CSE P548<br>

E N D

Presentation Transcript

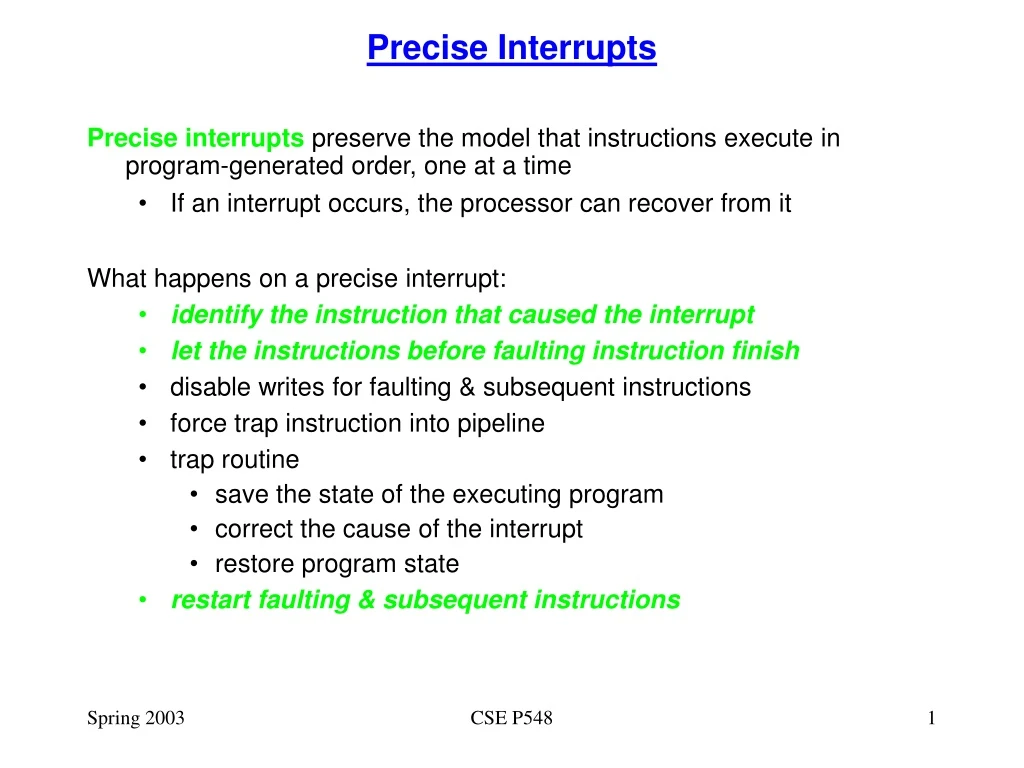

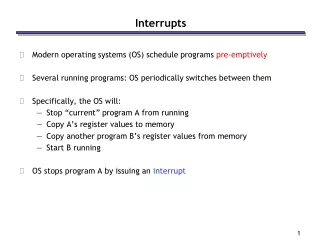

Precise Interrupts Precise interrupts preserve the model that instructions execute in program-generated order, one at a time • If an interrupt occurs, the processor can recover from it What happens on a precise interrupt: • identify the instruction that caused the interrupt • let the instructions before faulting instruction finish • disable writes for faulting & subsequent instructions • force trap instruction into pipeline • trap routine • save the state of the executing program • correct the cause of the interrupt • restore program state • restart faulting & subsequent instructions CSE P548

How Pipelines Complicate Interrupt Handling It’s fairly simple to maintain precise interrupts in the R3000 integer pipeline • one instruction fetched and executed each cycle • instructions executed in fetch order Still, there are issues…. Pipelines execute several instructions at once • how do you determine which one caused the exception? CSE P548

How Pipelines Complicate Interrupt Handling Simultaneous interrupts • 2 stages cause an interrupt at the same time • a solution: handle them in program order • still precise CSE P548

A 5-Stage Pipeline CSE P548

How Pipelines Complicate Interrupt Handling Interrupts out of order wrt sequential instruction execution • subsequent instruction causes an interrupt before a previous instruction • interrupts still must be handled in program order for precise interrupts A solution: interrupt handled before the write stage • interrupt recorded in a per-instruction bit vector which flows with it down the pipeline • interrupts for instruction in write stage are handled before it changes any state • restart all instructions in the pipeline CSE P548

divf FP exception multf not done add completed How Pipelines Complicate Interrupt Handling Multicycle operations in separate pipelines • some types • floating point operations • integer multiply & divide • can cause imprecise interrupts because operations don’t necessarily complete in program-generated order • example: • cannot restart interrupting & subsequent instructions because some have completed • a completed instruction may have overwritten one its source operands CSE P548

How Pipelines Complicate Interrupt Handling Dealing with imprecise interrupts • ignore the imprecise interrupt (IBM 360) • precise mode/imprecise mode (Alphas?)trade-off: correctness vs. performance • stall until no previous instruction will fault (Pentium Pro) • buffer writes until instructions complete • future file or shadow register; today called register renaming • history file (VAX)costs: additional registers & bypass logic to FUs CSE P548

How Multicycle Operations Complicate Pipelining Current structural hazards: multiple writes in the same cycle when instructions finish in a different order than their fetch order • track use of the write port & stall instructions in the decode stage if a conflict • set the bit in a shift register that is the number of cycles until the register file will be written • shift left each cycle • if this instruction’s bit is already set, stall • adv: check for all structural hazards in 1 place • disadv: shift register & write conflict logic • detect the hazard just before it occurs • stall before the common final stages • adv: easier to prioritize among instructions involved in the hazard • disadv: more complicated pipeline control because might need to check for structural hazards in multiple places CSE P548

ISA & Pipelines How instruction set architectures complicate pipelines: • variable cycle instructions cause: • more complicated hazard detection • more forwarding logic • more stalling • harder to implement precise interrupts • complex addressing modes cause: • WAR hazards from autoincrement • same problems as above from multiple memory accesses • self-modifying code • causes pipeline flush on address match between instruction being written & instruction later in the pipeline CSE P548