Mini-Project

Mini-Project. TeamMates. Project Goals. Security Systems using VHDL Temperature Control Fire Detection. VHDL History. VHDL resulted from the work done in the ‘70s and early ‘80s by the U.S Department of Defence. In 1986,VHDL was proposed as an IEEE standard

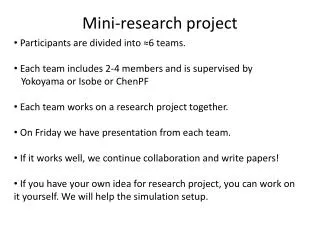

Mini-Project

E N D

Presentation Transcript

Mini-Project TeamMates

Project Goals • Security Systems using VHDL • Temperature Control • Fire Detection

VHDL History • VHDL resulted from the work done in the ‘70s and early ‘80s by the U.S Department of Defence. • In 1986,VHDL was proposed as an IEEE standard • VHDL has been at the heart of electronic design productivity since initial ratification by the IEEE in 1987 • Its roots are in the ADA language

Why Use VHDL • VHDL fueled modern synthesis technology and enabled the development of ASIC semiconductor companies • VHDL is a powerful language with numerous language constructs that are capable of describing very complex behavior • Unlike other programs its statements are inherently concurrent

Why Use VHDL • Ensures good tool design and data interoperability • Designers of programmable logic devices move to the use of hardware description languages as the basis of their design methodology • Could be used to create sophisticated electronic products

VHDL Overview • VHDL is a Hardware Description Language • Stands for Very High Speed Integrated Circuits Hardware Description Language • VHDL is intended for circuit synthesis as well as circuit simulation • VHDL is a standard ,technology/vendor independent language and is hence portable and reusable • Main applications of VHDL are in Programmable Logic Devices ( CPLDs, FPGAs, ASICs) FOR MORE INFO... List location or contact for competitive analysis (or other related documents) here

Design Flow • We start the design by writing VHDL code, which is saved with an extension .vhd and the same name as its ENTITY name • Benefits • First step in the synthesis is compilation • Compilation is the conversion of the high level VHDL language, which describes the circuit at the Register Transfer Level (RTL) into a netlist at the gate level. • Second step is Optimization • Performed for speed • Design can be stimulated at this stage • Finally software will generate the physical layout for a PLD/FPGA chip

Design Flow An example of a design flowchart is shown in the figure below:

VHDL Terms • Entity • Architecture • Configuration • Package • Bus • Attribute • Generic • Process • Driver

Phase 1 Phase 2 Phase 3 Jan Feb Mar Apr May Jun July Sep Oct Nov Dec Schedule • Review high-level schedule milestones here FOR MORE INFO... List location or contact for detailed schedule (or other related documents) here

Current Status • High-level overview of progress against schedule • On-track in what areas • Behind in what areas • Ahead in what areas • Unexpected delays or issues

Related Documents • Marketing plan • Location or contact name/phone • Budget • Location or contact name/phone • Post mortem • Location or contact name/phone • Submit questions • Location or contact name/phone