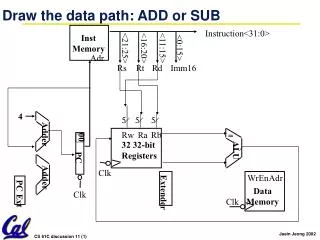

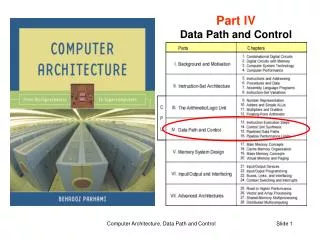

Draw the data path: ADD or SUB

Inst Memory. Adr. Adder. Adder. Draw the data path: ADD or SUB. Instruction<31:0>. <0:15>. <21:25>. <16:20>. <11:15>. Rs. Rt. Rd. Imm16. 4. 5. 5. 5. Rw. Ra. Rb. =. 00. 32 32-bit Registers. ALU. PC. Clk. WrEn. Adr. Data Memory. Extender. PC Ext. Clk. Clk. Inst

Draw the data path: ADD or SUB

E N D

Presentation Transcript

Inst Memory Adr Adder Adder Draw the data path: ADD or SUB Instruction<31:0> <0:15> <21:25> <16:20> <11:15> Rs Rt Rd Imm16 4 5 5 5 Rw Ra Rb = 00 32 32-bit Registers ALU PC Clk WrEn Adr Data Memory Extender PC Ext Clk Clk

Inst Memory Adr Adder Adder Draw the data path: ORI Instruction<31:0> <0:15> <21:25> <16:20> <11:15> Rs Rt Rd Imm16 4 5 5 5 Rw Ra Rb = 00 32 32-bit Registers ALU PC Clk WrEn Adr Data Memory Extender PC Ext Clk Clk

Inst Memory Adr Adder Adder Draw the data path: Load word Instruction<31:0> <0:15> <21:25> <16:20> <11:15> Rs Rt Rd Imm16 4 5 5 5 Rw Ra Rb = 00 32 32-bit Registers ALU PC Clk WrEn Adr Data Memory Extender PC Ext Clk Clk

Inst Memory Adr Adder Adder Draw the data path: Store word Instruction<31:0> <0:15> <21:25> <16:20> <11:15> Rs Rt Rd Imm16 4 5 5 5 Rw Ra Rb = 00 32 32-bit Registers ALU PC Clk WrEn Adr Data Memory Extender PC Ext Clk Clk

Inst Memory Adr Adder Mux Adder Draw the data path: Branch equal Instruction<31:0> <0:15> <21:25> <16:20> <11:15> Rs Rt Rd Imm16 4 5 5 5 Rw Ra Rb = 00 32 32-bit Registers ALU PC Clk WrEn Adr Data Memory Extender PC Ext Clk Clk

31 26 21 16 11 6 0 op rs rt rd shamt funct immediate op rs rt A Summary of the Control Signals See func 10 0000 10 0010 We Don’t Care :-) Appendix A op 00 0000 00 0000 00 1101 10 0011 10 1011 00 0100 add sub ori lw sw beq RegDst 1 1 0 0 x x ALUSrc 0 0 1 1 1 0 0 0 0 1 x x MemtoReg RegWrite 1 1 1 1 0 0 MemWrite 0 0 0 0 1 0 0 0 0 0 0 1 nPCsel OR: 001 ExtOp x x 0 1 1 x ADD: 010 ALUctr<2:0> Add Subtract Or Add Add SUB: 110 Subtract 0 1 0 0 0 ALUctr<2> 1 1 1 0 1 1 1 ALUctr<1> 0 0 1 0 0 0 ALUctr<0> R-type add, sub I-type ori, lw, sw, beq

Writing controls in Boolean formula • Express following variables in Boolean formula ofOPCode and Func • Add = OP[5]’*OP[4]’*OP[3]’*OP[2]’*OP[1]’*OP[0]’ *F[5] *F[4]’ *F[3]’ *F[2]’ *F[1]’ *F[0]’ • Sub = OP[5]’*OP[4]’*OP[3]’*OP[2]’*OP[1]’*OP[0]’ *F[5] *F[4]’ *F[3]’ *F[2]’ *F[1] *F[0]’ • Ori = OP[5]’*OP[4]’*OP[3]*OP[2]*OP[1]’*OP[0]’ • Lw = OP[5]*OP[4]’*OP[3]’*OP[2]’*OP[1]*OP[0] • Sw = OP[5]*OP[4]’*OP[3]*OP[2]’*OP[1]*OP[0] • Beq = OP[5]’*OP[4]’*OP[3]’*OP[2]*OP[1]’*OP[0]’

Writing controls in Boolean formula • Express following variables in Boolean formula ofAdd, Sub, Ori, Lw, Sw, Beq, OPCode, or Func • RegDst = Add + Sub • ALUSrc = Ori + Lw + Sw • MemtoReg = Lw • RegWrite = Add + Sub + Ori + Lw • MemWrite = Sw • nPCsel = Beq • ExtOp = Lw + Sw • ALUctr<2>= Sub + Beq • ALUctr<1>= Add + Sub + Lw + Sw + Beq • ALUctr<0>= Ori