Variation Aware Application Scheduling in Multi-core Systems

Variation Aware Application Scheduling in Multi-core Systems. Lavanya Subramanian, Aman Kumar Carnegie Mellon University {lsubrama, amank}@andrew.cmu.edu. Document Map. Motivation Leakage Power and Frequency Variations in CMP Problem

Variation Aware Application Scheduling in Multi-core Systems

E N D

Presentation Transcript

Variation AwareApplication Scheduling in Multi-core Systems Lavanya Subramanian, Aman Kumar Carnegie Mellon University {lsubrama, amank}@andrew.cmu.edu

Document Map • Motivation • Leakage Power and Frequency Variations in CMP • Problem • Application scheduling exploiting frequency variation and leakage per core in CMPs • Related Work • Proposed Scheme • Unified Power Performance Approach • Milestones

Motivation • Variations in chip multi processors are a major concern. There are two components to this: • The die-to-die component. • The within-die component. At the transistor/device level, these are variations in • Leff • Vth • These variations in Leff and Vth translate into frequency and leakage current variations at the micro-architecture level.

Motivation (contd…) Why a UNIFIED Power/Performance approach?? For cores that can operate at a specific maximum frequency, there is a wide variation in the leakage profiles. Analogously, for cores that have a certain leakage power, there is a wide spread in the maximum frequency characteristics. [3]

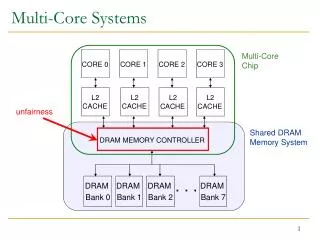

Problem • The perspective of a chip multi processor being a homogenous set of cores is hence not a practical one. • A CMP has to be relooked as: • a collection of heterogeneous cores • each core operating at different frequency • each core with a different power profile

Related Work • Work being done at UIUC, talks about a set of scheduling algorithms taking either power or performance in account but not both together.[1] • The basic power efficiency inclined algorithm (VarP) tries to map applications onto the least leaky cores. • The enhanced version of this (VarP+AppP) tries to map the highest dynamic power consuming applications onto the least leaky cores. • Similarly, the performance centric algorithms (VarF)map applications onto the fastest cores.

Proposed Scheme • Rank the cores in the order of the maximum frequencies. • Obtain the static leakage power number for each core (profiled statically at a nominal temperature) • Rank the applications in the order of dynamic power (obtained by static profiling on a core) • For each application, starting from the highest dynamic power one, map the application onto the core with the highest frequency, with the least leakage. This could be achieved by sorting the cores in frequency and leakage bins/levels.

Milestones • Milestone 1.1: • Building variability information into the CMP simulator. • Static profiling of applications. • Milestone 2: • Building a scheduler into the CMP simulator. • Milestone 3: • Implementing and analyzing the proposed scheme against the baseline algorithms.

References [1] R. Teodorescu and J. Torrellas. Variation-aware application scheduling and power management for chip multiprocessors. In ISCA’08: Proceedings of the 35th annual InternationalSymposium on Computer Architecture, 2008 [2] Y. Abulafia and A. Kornfeld. Estimation of FMAX and ISB in microprocessors. IEEE Transactions on VLSI Systems, 13(10), Oct 2006 [3] S. Borkar et. al., “Parameter variations and impact on circuits and micro-architecture,” Proc. DAC 2003, pp. 338-342