Force-Directed Scheduling

380 likes | 545 Views

Force-Directed Scheduling. Sune Fallgaard Nielsen Informatics and Mathematical Modelling Technical University of Denmark Richard Petersens Plads, Building 321 DK2800 Lyngby, Denmark. Overview / Agenda. Motivation Introduction Defining problem and model Solution Results Conclussion.

Force-Directed Scheduling

E N D

Presentation Transcript

Force-Directed Scheduling Sune Fallgaard Nielsen Informatics and Mathematical Modelling Technical University of Denmark Richard Petersens Plads, Building 321 DK2800 Lyngby, Denmark

Overview / Agenda • Motivation • Introduction • Defining problem and model • Solution • Results • Conclussion [M-1] High-Level Synthesis

Motivation • The mapping from a behavioral model to a physical Register-Transfer level description is a NP-complete problem. • Therefore an exhaustive comparison on all possible solutions is infeasible. • An algorithm finding an efficient mapping is required. [M-1] High-Level Synthesis

Introduction • The paper was written in 1989. • The interest on High-Level Languages like VHDL is increasing at that time. • Synthesis tools capable of generating a RTL realization from a behavioral model is needed. [M-1] High-Level Synthesis

Mathematical domain synthesis create an alogorithm to solve the problem create a model of the physical problem Transform the optimized model back to the physical domain specification implementation specification implementation design Physical domain Introduction [M-1] High-Level Synthesis

Mathematical domain synthesis create an alogorithm to solve the problem create a model of the physical problem Transform the optimized model back to the physical domain specification implementation specification implementation design Physical domain Introduction [M-1] High-Level Synthesis

Defining problem and model • The problem: For a given function, find an optimal solution. An optimal solution can be constrainted by area-, power-, performance- or flexibility requirements depending on the application. • The model: Scheduling : Determine for each operation the time at which it should be performed without violating any precedence contraints. [M-1] High-Level Synthesis

Solution Common Approach New Approach List Scheduling Force-Directed Scheduling Resources given Time contraints given Minimize delay Minimize required resources [M-1] High-Level Synthesis

Solution Common Approach New Approach List Scheduling Force-Directed Scheduling Resources given Time contraints given Minimize delay Minimize required resources [M-1] High-Level Synthesis

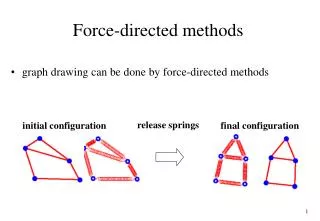

Force-Directed Scheduling • The Force-Directed Scheduling approach • reduces the amount of: • Functional Units • Registers • Interconnect • This is achieved by balancing the concurrency of operations to ensure a high utilization of each unit. [M-1] High-Level Synthesis

Force-Directed Scheduling • The Force-Directed Scheduling algorithm consists of 3 steps: • Determine a time frame of each operation • Create a distribution graph • Calculate the force (a new metric) [M-1] High-Level Synthesis

Scheduling – An example • Solve the differential equation y’’ + 3zy’ + 3y = 0 • This can be calculated using this iterative algorithm while(z < a) repeat zl := z + dz; ul := u – (3 · z · u · dz) – (3 · y · dz); yl := y + (u · dz); z := zl; u := ul; y := yl; [M-1] High-Level Synthesis

Scheduling – An example Data-Flow and Control-Flow Graphs ASAP Scheduling ALAP Scheduling [M-1] High-Level Synthesis

Scheduling – An example Data-Flow and Control-Flow Graphs ASAP Scheduling ALAP Scheduling [M-1] High-Level Synthesis

Scheduling – An example Step 1 : Determine a time frame of each operation Error in Figure [M-1] High-Level Synthesis

Scheduling – An example Step 2 : Create a distribution graph DG(1) = 2.833 DG(3) = 0.833 DG(2) = 2.333 DG(4) = 0 [M-1] High-Level Synthesis

Scheduling – An example Step 3 : Calculate the force (a new metric) A metric called force is introduced. The force is used to optimize the utilization of units. A high positive force value indicates a poor utilization. [M-1] High-Level Synthesis

Scheduling – An example Step 3 : Calculate the force (a new metric) Free Fixed [M-1] High-Level Synthesis

Scheduling – An example Step 3 : Calculate the force (a new metric) With the operation x’ in control-step 1. Poor utilization DG(1) = 2.833 DG(3) = 0.833 DG(2) = 2.333 DG(4) = 0 [M-1] High-Level Synthesis

Scheduling – An example Step 3 : Calculate the force (a new metric) With the operation x’ in control-step 2. (x’’ must be in control-step 3) Direct force (calculated as before) Indirect force (on x’’ in control-step 3) Good utilization DG(1) = 2.833 DG(3) = 0.833 DG(2) = 2.333 DG(4) = 0 [M-1] High-Level Synthesis

Scheduling – An example By repeatedly assigning operations to various control-steps and calculating the force associated with the choice several force values will be available. The Force-directed scheduling algorithm chooses the assignment with the lowest force value, which also balances the concurrency of operations most efficiently. [M-1] High-Level Synthesis

Force-Directed Scheduling • The Force-Directed Scheduling approach • reduces the amount of: • Functional Units • Registers • Interconnect By introducing Registers and Interconnect as storage operations, the force is calcuted for these as well. The 3 steps of the algorithm are carried out for these operations also. [M-1] High-Level Synthesis

Force-Directed Scheduling [M-1] High-Level Synthesis

Force-Directed Scheduling Introducing Registers and Interconnect as operations. Since the Registers and Interconnect area consumption is reduced in solution b, it might be optimal. [M-1] High-Level Synthesis

Force-Directed List Scheduling List Scheduling Force Directed Scheduling Resources given Time contraints given Minimize delay Minimize required resources If the problem is the other way around, ie. if the resources are given a Force-Directed List Scheduling algorithm can be applied. [M-1] High-Level Synthesis

Force-Directed List Scheduling • The Force-Directed List Scheduling utilizes the • strengths of the: • Force-Directed Scheduling and • List Scheduling Force-Directed List Scheduling is similar to List Scheduling except force is the priority function, not mobility. [M-1] High-Level Synthesis

Force-Directed List Scheduling List Scheduling Force-Directed List Scheduling Force is a better metric Mobility is a poor metric We have 1 adder and 1 multiplier [M-1] High-Level Synthesis

Results Test Application : Fifth-order Elliptic Wave Filter Many optimal results, depending on the application One result, ASAP is not optimal. xp is a pipelined multiplier [M-1] High-Level Synthesis

Results – The Design Space The Force-Directed List Scheduling gives better means for exploring the design space. It offers many results and depending on the application the designer can choose to use more or less resources and see what implications it will have on the delay. [M-1] High-Level Synthesis

One more optimization The Force-Directed List Scheduling is implemented in a system called HAL. HAL also uses techniques called register merging and multiplexer merging. These techniques minimizes the cost on registers and interconnections. [M-1] High-Level Synthesis

Results Comparison on various syntesis tools normalized to HAL86 Test Application : Differential Equation Non-pipelined Multiplier Pipelined Multiplier [M-1] High-Level Synthesis

Results Physical unit and interconnection requirements Test Application : Wave Filter [M-1] High-Level Synthesis

Conclussions • The Force-Directed Scheduling and Force-Directed List • Scheduling algorithms allows the designer to explore the • design space. • By taking into account the cost of interconnection, registers • and multiplexers a more precise algorithm is realized. • The HAL system, using these algorithms, shows promising • results compared to other systems. [M-1] High-Level Synthesis