Understanding AT94K Configuration Modes for FPGA Development

This document outlines the configuration modes for the AT94K FPGA series, detailing the functionalities of each mode controlled by M0 and M2. It explains Mode 0 (Master Serial via Configurator) and Mode 1 (Slave Serial Cascade) operations, including dedicated and dual-use pins. The document covers varying clock rates, parallel programming capabilities, and specific configurations for CacheLogic applications. Additionally, it highlights resources available for developers, including a comprehensive development board, design verification processes, and tools for designing with the AT94K FPGA.

Understanding AT94K Configuration Modes for FPGA Development

E N D

Presentation Transcript

AT94K Training AT94K Configuration Modes Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 Hotline (408) 436-4119 fpga@atmel.com OR configurator@atmel.com

Configuration Modes • 2 Configuration Modes controlled by M0 and M2 • Mode 0: Master serial ( by Configurator ) • Mode 1: Slave Serial Cascade ( External MCU )

AT94K Configuration I/O • Dedicated Pins (all modes) • M2, M0, RESET, CON, CCLK. • Dual Use Pins • INIT (all modes) • CSOUT, CHECK, CS1, CS0, A(23:0), D(15:0), HDC, LDC A (Active) O (Optional)

Mode 0 • 1, 2, 4 or 8 MHz internally-generated CCLK set through Bitstream options • Configurator RESET pin may be tied to either FPGA RESET or INIT pin • Mode 1M2 M00 0

Mode 1 • External clocking up to 40 MHz • Microprocessor- or EEPROM-driven • Mode 1M2 M0 • 0 1

Mode 1 Parallel • Allows independent programming of multiple FPGAs in parallel with the same data • Mode 1 M2 M0 • 0 1

Mode 1 Cascade • Uses CS0 to propagate chip select between cascaded FPGAs; Xilinx devices propagate data • M2 M0 • Mode10 1

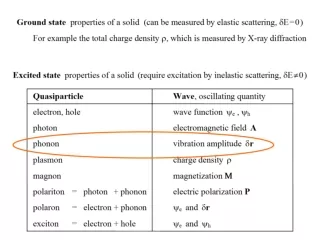

AT94K Example Bitstream Serial data is read in MSB first. Byte/word entries above are shown MSB<->LSB. Not applicable to Mode 4.

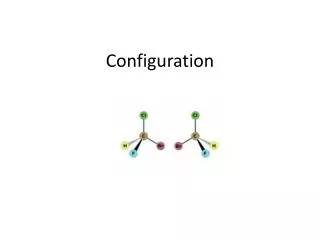

Mode designed for CacheLogic applications Device treated as an SRAM by the system Microprocessor treats FPGA as memory mapped I/O. Simple 24 bit Address and 8 bit Data structure. Cache Logic Mode LSB MSB X Address Tag Data Z Address Y Address 8 Bits 8 Bits 8 Bits 4 Bits 4 Bits 32 Bit word defines address and data Information for one byte per clock cycle 0 31 or 39

Memory map is architected to support CacheLogic Applications. Memory Map Pages are all dissociated. Writing data to one structure has NO impact on any other structure. Key requirement for CacheLogic. Simple 32 bit interface and 33MHz clocking allow very rapid caching of logic functions. Symmetrical FPGA architecture results in simple and predictable CacheLogic designs. Each memory byte has a unique memory map location and can be individually addressed. Data can be loaded x8 for faster reconfiguration. In full bitstream, X, Y, Z, Tag information is handled by the on-chip control logic. Design verification of AT94K FPSLIC devices Built-in support for Configuration processes Mode 0 Mode 1 AT94K Memory Map and CacheLogic

Design verification of AT94K FPSLIC Built-in support for Configuration processes Mode 0 Program Configurator Boot from Configurator Mode 1 Download direct to FPGA with CS0 ATDH40M Development Board

FPSLIC Starter KitATSTK94 NEW • Text book to take customers step by step through the design process • System Designer tool for 4 months trial period • Synthesis/VHDL Simulator/Co-verification • AVR studio debugger • Place and Route IDS7 • IAR and Imagecraft C compiler( 1 month trial period) • Comprehensive development board • Design examples • AT94K40 • AT17LV010 Configurator • 2 Serial Ports • Programmable switches & LEDs • ISP cables for programming configurator