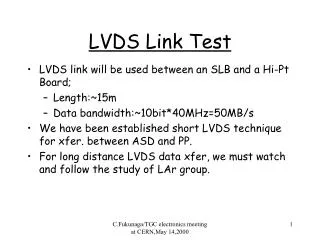

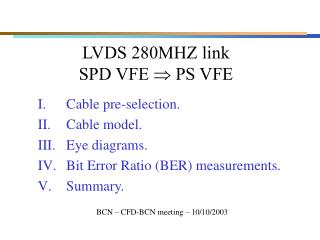

LVDS Link Test

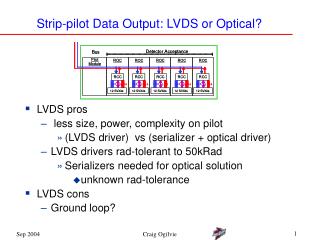

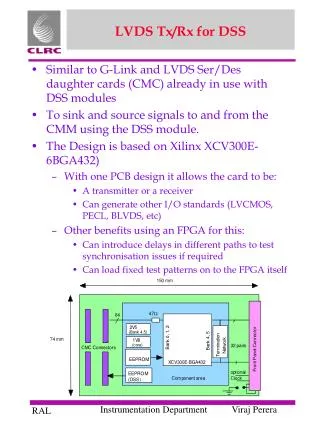

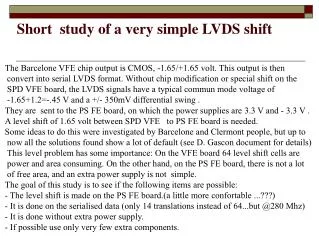

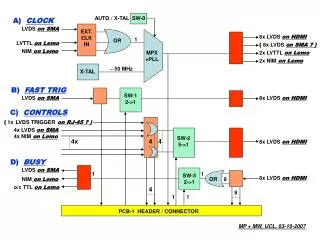

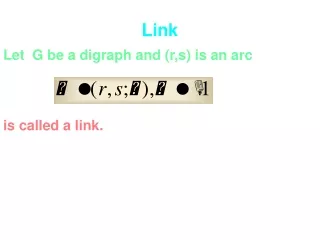

This document outlines the design and testing of a Low Voltage Differential Signaling (LVDS) link used for data transfer between a SLB and a Hi-Pt Board over a distance of approximately 15 meters, enabling a data bandwidth of 50 MB/s. It summarizes our established short-distance LVDS technique for efficient transfer between ASD and PP. Additionally, it highlights the importance of following advancements in long-distance LVDS data transfer as discussed in a study by C. Fukunaga at the CERN TGC electronics meeting in May 2000, and presents a detailed LVDS development schedule.

LVDS Link Test

E N D

Presentation Transcript

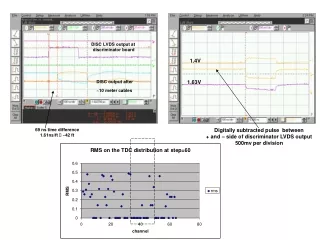

LVDS Link Test • LVDS link will be used between an SLB and a Hi-Pt Board; • Length:~15m • Data bandwidth:~10bit*40MHz=50MB/s • We have been established short LVDS technique for xfer. between ASD and PP. • For long distance LVDS data xfer, we must watch and follow the study of LAr group. C.Fukunaga/TGC electronics meeting at CERN,May 14,2000

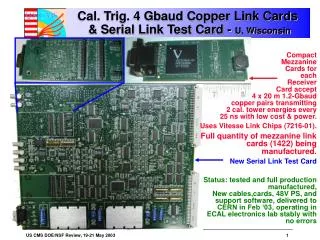

LVDS Development Schedule • Setup of a Test Bench (Jul.2000) • Operation experience of • Serializer and Deserialiser • Cable, Cable length (Aug.2000) • Study of Equalizer(Compensation) Effect (Sept.2000) • Overall study with parallel link cable and clock distributed by TTCrx (Oct.2000) C.Fukunaga/TGC electronics meeting at CERN,May 14,2000