Global Trigger Environment

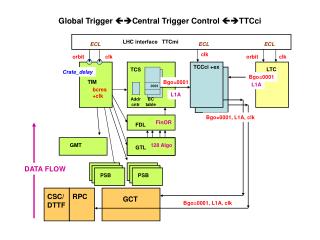

Global Trigger Environment. Global Trigger Overview. PSB Input synchronization GTL Logic calculation FDL L1A decision TIM Timing GTFE Readout. Global Trigger Crate. Pipelined synchronizing buffer PSB. PSB 6 channel prototype. Algorithm Logic.

Global Trigger Environment

E N D

Presentation Transcript

Global Trigger Overview PSB Input synchronization GTL Logic calculation FDL L1A decision TIM Timing GTFE Readout

Algorithm Logic Initial step: Particle and Delta Conditions The first are applied to a group of objects. The conditions are: ET or pT thresholds, h/f-windows, bit patterns for isolation, quality, charge, and spatial correlations (Dh, Df) between objects of the same type. Delta Conditions calculate spatial correlations between different objects. Particle Condition for 2 back-to-back isolated electrons Particle Condition for 2 back-to-back isolated opposite-sign muons with MIP bits set

Algorithm Logic Next step: Actual algorithm calculations. Logical combinations (AND-OR) of objects are determined.

Setup- and Placement Program generating VHDL code for the Condition chips Wiring of input channels for 6U prototype boards

Setup- and Placement Program Event Generator

Condition to find 2 isolated electrons/photons with spatial correlation <== Setup file

Status of Global Trigger September 2000 • Custom backplane and PSB input prototype exist. • GTL-prototype: 4 m, 4x4 calorimeter channels • New structure of the prototype similar as on the final 9U board • uniform structure, smaller latency, flexibility, but design more complicated • Condition Chips :Each receives two thirds of the input channels • Conditions, Spatial conditions, Pre-Algorithms, Algorithms • Algo Chips: Algorithms • VHDL design ==> fixed VHDL code • Predefined Templates, Condition types, I/O-pins • Setup and Placement Software ==> variable VHDL code • Wiring of Input Channels and of algorithm bits to output pins • Definition of Conditions //Condition types as building blocks. • Definition of Algorithm AND-OR logic // product terms, inversion • aim for ===>Automated Chip design • Event Generator Software • Board layout: Placement, connectors....

Status of Global Trigger September 2000 • FDL board: Definition of functions ongoing • TCS board:Partitioning; definition of functions • JTAG software from JTAG Technology • infrastructure, interconnection, cluster tests done • problems with programming of FPGAs by JTAG • PSB module tested: 25% of connections can be tested • BGA Solder station for Fine Line BGA (1mm grid) chips • 256, 484 pins...ok; • 672 pins...Tests to find optimal solder parameters

Schedule 2001 • GTL-prototype: • VHDL design finished and prototype board produced • delay Nov 2000 ==> Jan 2001 • Software for Design and Tests until March 2001... • FDL board: • Functions defined and top-down design done until Nov 2000. • FPGA chips designed and FDL board built until Nov 2001. • GMT : Conceptual design until Nov 2000 • define and simulate final algorithms • JTAG software and tests: available until Dec 00...already working

Milestones 1999, 2000-2004 • D431 - June 1999 • PSB_6U prototype production Status: Board tested. • BACK6U design Status: done • D432 – Nov 1999 milestone changed • BACK6U production Status: Board in use. • D433 - June 2000 • GTL_6U design Status: Delay due to redesign • D434 – Nov 2000 Trigger Logic Functions tested • GTL_6U tested; Status: Delay • FDL_9U design • Combined logic test: Backplane + PSB + GTL • Conceptual GlobalMuon Trigger design • D435 - Nov 2001 Complete Logic Pipeline tested • Combined Prototype test: Backplane + PSB + GTL+FDL • D436 - June 2003 24-channel Global Trigger available • D437- Nov 2003 Global Muon Trigger available • D438 - Nov 2004 32-channel Global Trigger available