系统级设计描述语言 SystemC

621 likes | 1.43k Views

系统级设计描述语言 SystemC. 第一部分 为什么用 SystemC 做片上系统设计?. 教材: 陈曦 徐宁仪《 SystemC 片上系统设计》,科学出版社,2003 本课件大部分内容参考此书,仅作为大学教学之用, 请勿用于商业. 徐宁仪 xuny97@mails.tsinghua.edu.cn xuny @ smth. 版权所有 200 4. 课程主要内容. 共讲4次 ,争取讲清楚 Why&How , 重点是概念. 内容包括: 为什么用 SystemC 做片上系统设计? SystemC 基本语法* SystemC 行为建模基础*

系统级设计描述语言 SystemC

E N D

Presentation Transcript

系统级设计描述语言SystemC 第一部分 为什么用SystemC做片上系统设计? 教材:陈曦 徐宁仪《SystemC片上系统设计》,科学出版社,2003 本课件大部分内容参考此书,仅作为大学教学之用, 请勿用于商业 徐宁仪 xuny97@mails.tsinghua.edu.cn xuny @ smth 版权所有 2004

课程主要内容 • 共讲4次,争取讲清楚Why&How, 重点是概念 • 内容包括: • 为什么用SystemC做片上系统设计? • SystemC基本语法* • SystemC行为建模基础* • SystemC交易级建模与通信细化* • SystemC 方法库 • Master/Slave库 • 验证库

第一部分 为什么用SystemC做片上系统设计?

内容 • 概念- IP核,片上系统, • 片上系统设计面临的挑战 • 设计描述语言的发展,设计描述语言的分层 • SytemC介绍 • 内容 • 优点 • 实践 • 工具 • 最新进展

IP核 • IP(Intellectual Property)就是常说的知识产权。 • 美国Dataquest咨询公司将半导体产业的IP定义为用于ASIC、ASSP、PLD等当中,并且是预先设计好的电路功能模块。 • 软IP (Soft Core) 用计算机高级语言的形式描述功能块的行为,但是并不涉及用什么电路和电路元件实现这些行为。软IP增大了IP的灵活性和适应性。 • 固IP (Firm Core) 是完成了综合的功能块,有较大的设计深度,以网表的形式提交客户使用。 • 硬IP (Hard Core) 提供设计的最终阶段产品:掩膜。 • Eg. • CPU • MPEG-2, MPEG-4, MP3 • PCI, USB, IC card • RAM, FIFO, PLL…

什么是片上系统(System-on-a-chip) • SoC的主要特征 • 实现复杂系统功能的VLSI • 采用深亚微米工艺技术 • 使用一个以上嵌入式CPU/数字信号处理器(DSP) • 外部可以对芯片进行编程 • 主要采用第三方IP进行设计 • SoC的主要价值所在—缩短产品的上市周期 • 定义: SoC是在一个芯片上由于广泛使用预定制模块IP(Intellectual Property)而得以快速开发的集成电路。 • 方法学角度 • SoC是一套极大规模集成电路的设计方法学,包括IP核可复用设计/测试方法及接口规范、系统芯片互联集成设计方法学、系统芯片验证和测试方法学等。 *Ref: Rochit Rajsuman, System-on-a-chip: Design and Test

实例1 – 数字电视广播接收系统主芯片 *Ref: www.xilinx.com

实例2-手持移动终端 *Ref: Arie, Bernstein, DAC2004

片上系统设计的挑战 • 集成电路技术包括设计、制造、封装、测试。 • 瓶颈在于设计。 • SoC复杂度在提高 • 时钟频率,多处理器,多级缓存,复杂的DMA,协处理器,深度流水线… • 约需要300mm (man month) • 软件复杂度在提高 • 代码长度在提高, 多处理, 高密度的通道.. • 约需要400mm (man month) (比硅设计需要更多的人力) • SoC要求迅速表达概念,探索各种结构,功能以优化设计

片上系统设计的挑战 – 体系结构探索2 *Ref: Pierre, Paulin, DAC2004

加速SoC设计的方法 • IP核的复用 • 高层次综合 • 发展新的设计方法学 • 新的设计方法学依赖于新的设计语言和设计工具

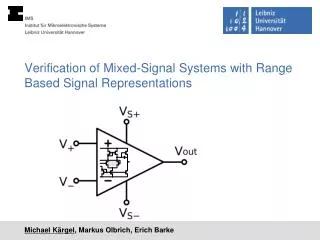

片上系统对设计/描述语言的要求 • 高仿真速度和建模效率 • 时序和行为可以分开建模 • 支持软件和硬件建模 • 支持基于平台的设计 • 支持从系统级到门级的无缝过渡 • 支持系统级调试和系统性能分析等 VHDL和Verilog HDL无法满足要求

设计描述语言的发展 • 两个发展方向 • 扩展VHDL与Verilog HDL,比如Superlog、SystemVerilog • 扩展C/C++,比如SpecC,SystemC • 两种重要语言 • SystemC,支持完整的系统设计与验证,=C++ +HDL • SystemVerilog,支持验证和寄存器传输级设计的最好语言,=扩展的Verilog+Vera

SystemC – 提出 • 1999.9 美国加州Saint Jose的嵌入式系统会议 • SystemC开放标准. http://www.systemc.org • 由OSCI (Open SystemC Initiative )组织推动

SystemC介绍 – 语言架构 • SystemC本质上是在C++的基础上添加的硬件扩展库和仿真核

SystemC– 描述层次 • SystemC不仅仅是一种新的硬件描述语言,而是一种系统描述语言

1 2 Verilog VHDL 3 Daisy Mentor Valid SystemC– 描述层次 System Level RTL Level Gate Level 1980s 1990s 2000s

SystemC– 描述层次 • 寄存器传输级(RTL) • 硬件实现层, 关注信号/比特,时钟周期精确。如组合逻辑,触发器,计数器,状态机等 • VHDL和Verilog的主要描述层次 • 时钟周期精确级 • 保留时钟周期精确的行为,去掉底层实现细节。主要描述交易(transaction)。交易描述的是数据的传输本身(源,目的,数据,长度),而不描述如何实现具体的握手协议。 • 具有基于时钟的执行语法,能够直接映射到寄存器级传输的信号。 • 仿真速度约为10-100KHz,可用于系统验证.

SystemC– 描述层次 • 带时间信息的编程级(PVT= Programmer View + Timing) • 对编程级描述加入时间信息。 • 单个数据或者数据块作为一个传输。 • 时间信息被建模为“完成任务所需时间”,而不是“完成任务的每个时钟周期的行为”。 • 数据的通信在时钟精确级建模,以对系统体系结构对性能的影响进行建模。 • 仿真速度为1 – 5 MHz,可以用来进行系统性能评估和设计空间探索。 • 编程级(Programmer View) • 精确到比特的系统描述,可以为软件编程人员所用。 • 点对点的通信,不考虑具体总线的架构。 • 仿真速度为10 - 100MHz:足够用于系统的评估和软件开发 • 算法级 • 系统的功能性表示,与特定的体系结构无关. • 描述语言取决于应用的领域 • Matlab: 通信信号处理,图像处理, 控制… • UML:软件工程 • SDL:通信协议

SystemC– 描述层次 • 高层: • 优化更有效率 • 底层 • 面向实现 • SystemC的描述层次适于进行体系结构的探索

C/C++ System Level Model VHDL/Verilog Analysis Simulation Results Synthesis Rest of Process SytemC介绍 – 设计流程 传统的设计流程 手工转换 Refine

SystemC Simulation Refinement Synthesis Rest of Process SytemC介绍 – 设计流程 有了SystemC的设计流程

SystemC介绍 –设计流程典型System-on-Chip设计流程 需要多个设计周期 系统设计没有标准化 需要建立硬件平台,软件设计开始比较慢 各个设计接口处容易出现问题

SystemC介绍 –设计流程SystemC带来的新的解决方案 • (1)在RTL设计之前,创建可执行的Golden Architecture。 • 使用“虚拟系统原型”进行早期的系统结构探索和软件开发。 • 使用系统级测试平台进行RTL的模块级验证 • (2)通过IP重用和原型测试将Golden Architecture转化成Golden RTL

SystemC介绍 –设计流程新的设计流程 使用可执行的系统设计规范,能够在系统结构模型上运行软件,从而具有软硬件并行设计的能力,减少了得到Golden RTL的时间。

两种流程的关键区别 • 原有流程:系统结构收敛和RTL收敛都在RTL模型上完成。 • 新流程:系统结构收敛在Transaction Level完成,RTL收敛在RTL模型上完成。

Transaction Level vs. RTL • 交易级建模 • 系统模型中两个组件的一次数据交换. • 在片内总线架构之上,主要对各功能模块之间的并行通信进行建模。不考虑具体总线握手时序,资源占用等情况. • 优点 • 更高级别的抽象能力 • 更快的模拟速度(比RTL级建模快100倍以上) • 语言: • RTL:Verilog HDL, VHDL, SystemC • TL: SystemC,SDL

SystemC介绍 – 仿真 基于SystemC的指令集仿真 SystemC Simulation ARM Core Bus interface ARM Core Simulator Peripheral Models Bus-cycle transactions Bus-cycle pin transactions RDI SystemC让软硬件协同设计和验证更容易 Debugger

SystemC与第三方工具/语言的结合 • SystemC+UML • SystemC+MATLAB

为什么SystemC+UML • UML是可视化的设计规范语言,包括类的关系图、协作图、状态转移图等 • UML广泛使用于软件和嵌入系统设计中,软件工程师普遍掌握 • SystemC本质上是C++,可以用UML来规范 • UML+SystemC在业界已经开始使用 • 目前的问题是不能进行UML<->SystemC的双向转换,UML2.0将会支持 • 所以……SystemC+UML=最好的设计规范语言+最好的系统设计语言

为什么SystemC+MATLAB? • MATLAB有良好的用户界面,强大的计算功能和多元的可视化函数 。 • MATLAB为广大工程师所掌握,利用它可以迅速构建算法模型。 • MATLAB提供了C接口,与SystemC很容易结合。 • 利用MATLAB来验证SystemC算法模块,分析浮点算法与定点实现之间的性能损失。 • 所以……MATLAB+SystemC=一种优良的算法(定点/浮点)性能分析途径

关于SystemC的几个关键澄清 • SystemC 的主要目的是实现用单一语言完成设计规范、系统体系结构分析、验证平台和行为模型。 • 传统硬件描述语言的C接口不支持硬件设计中的并发性、层次性和互连。 • 现在的很多设计都从算法开始,SystemC比C/C++更适合对算法的描述和分析。 • 用SystemC的行为模型描述的算法模块比RTL模块快10~100倍。 • SystemC的更大价值在于其提供高层次设计流程。行为级综合工具经过多年的发展渐渐成熟,SystemC和行为综合工具结合的设计方法将会大大提高设计和验证效率. SystemC特别为行为综合设计的语法将使它成为非常适合行为级综合的设计语言。

SystemC介绍小结 • 开放的标准和组织 • 语言架构:一个C/C++类库和仿真内核,用来描述和仿真HW/SW/System。是C++语言的超集。 • 描述层次: 系统级描述语言 • 设计流程: 软硬件协同设计 • 扩展能力: 易于与第三方语言工具结合

SystemC,真的行么?(2003年) • 我们的经验:深圳清华大学研究院EDA实验室已经用SystemC设计了数字音频芯片并且流片了! • 别人的经验:阿尔卡特用SystemC设计的无线局域网802.11 MAC+基带芯片! • 大唐飞利浦去年招聘懂Cocentric System Studio+SystemC 的工程师呢! • 今年东方通信在水木上招聘懂SystemC的兼职!

SystemC in 2004 • 41st Design Automation Conference • "SystemC Here and Now“ technical symposium • “System-Level Design: Six Success Stories in Search of an Industry” • Pierre Paulin, STMicroelectronics • Arie Bernstein, Intel Corp. • Reinaldo A. Bergamaschi, IBM Corp. • Ramesh Chandra, QUALCOMM • Raj Pawate, Texas Instruments • Mohamed Ben-Romdhane, Conexant

SystemC的设计工具 • AccurateC --SystemC语法和设计规则检查 • A|RT Builder--SystemC到HDL的转换 • MaxSim--SOC建模和验证工具 • NC-SystemC--仿真器 • Cynthesizer/SystemC Compiler--SystemC综合器 • Synopsys和XILINX联合开发Virtex II FPGA的系统设计工具,本质上等于CCSS+FPGA Compiler II+现有FPGA 布局布线工具 • Visual Elite/SPW4.8/Cocentric System Studio/C-Bridge…… SystemC开发工具已经覆盖系统设计到RTL设计、综合到验证的全部集成电路设计前端!

总之 • 实践已经证明了SystemC的好处,成为事实标准。 • SystemC已经被提交到IEEE,即将成为真正的标准。 • SystemC设计工具广泛存在。 • SystemC是复杂片上系统设计的最佳语言 • SystemC是未来集成电路设计和电子系统设计工程师必备语言之一

参考资料 • 陈曦 徐宁仪《SystemC片上系统设计》,科学出版社,2003.10(本课程教材) • OSCI. SystemC User Guide. http://www.systemc.org • OSCI. SystemC Functional Specification. http://www.systemc.org • OSCI.SystemC Language Reference Manual. http://www.systemc.org • IEEE上关于SystemC的文章

本章结束 • Q & A时间

SystemC与SystemVerilog • SystemC是ARM/Synopsys/Cadence/CoWare/富士通等50几家大公司共同支持开发的语言。严格来讲并不是新语言,而是C++的一个库。SystemC语言经过发展已经成为一种稳固的语言,系统架构师可用来创建完整的软硬件体系架构,SystemC已经被提交到IEEE。 • SystemVerilog的背景:Open Verilog International和VHDL Internantional 合并成立Accellera,该组织提出了SystemVerilog。SystemVerilog的前景尚有不确定性(工具的支持和IEEE标准的竞争)。

SystemC与SystemVerilog是你死我活的竞争对手么? • No! ,在真实设计流程中的经验清楚地表明,这两种语言非但不是相互对立,而且还是一种互补的关系 • SystemC和SystemVerilog在不同的设计领域中,分别有各自的特点。两种标准的结合,将从系统规范、门电路布局直至设计验证,为设计人员提供一种可供选择的综合语言环境。 • “SystemVerilog将会成为SystemC进一步发展的基石。”