Cadence 工具简介

Cadence 工具简介. 王智鹏. 一、浏览电路. Cadence virtuoso 基于 linux 操作系统,主要包括 电路系统设计工具、版图设计工具 和 版图验证工具 。软件启动后,会看到全局管理窗口 ——CIW. 在 CIW 窗口中点击“ Tools” ,选择“ library manager” 打开库文件管理器。并从中单击选择所需的 library—cell—view ,双击“ schematic” 打开目标电路图。. 在 schematic editing 窗口浏览分析电路。常用指令及其快捷键. PMOS. NMOS. 二、绘制版图.

Cadence 工具简介

E N D

Presentation Transcript

Cadence工具简介 王智鹏

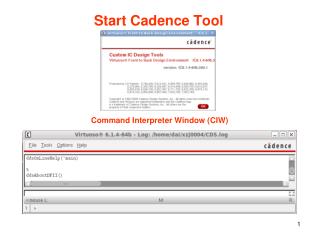

一、浏览电路 • Cadence virtuoso 基于linux操作系统,主要包括电路系统设计工具、版图设计工具和版图验证工具。软件启动后,会看到全局管理窗口——CIW

在CIW窗口中点击“Tools”,选择“library manager”打开库文件管理器。并从中单击选择所需的library—cell—view,双击“schematic”打开目标电路图。

在schematic editing 窗口浏览分析电路。常用指令及其快捷键

PMOS NMOS

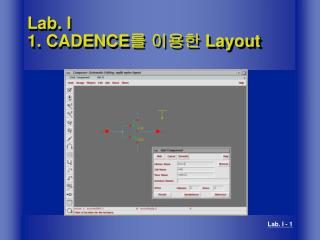

二、绘制版图 1、新建版图文件: 文件库名 文件名 • 在库文件管理器“cell”一栏中选中需要设计版图的电路文件 • 在库文件管理器菜单中依次点击file—new—cell view,出现新建文件窗口 文件类型 选用工具

注意,版图文件的library name(库名)、cell name(单元名)必须与电路文件相同。点击“tool”右侧的工具选择按钮,选择“virtuoso”,点击OK,完成新文件创建。

2、版图编辑界面 • 版图编辑窗口中,顶端显示文件所对应的库名、单元名、文件类型信息。 单元名 文件类型 库名

版图编辑窗口由icon menu(图标菜单)、menu banner(菜单栏)、status banner(状态栏)三部分组成。 状态栏 菜单栏 图标菜单 • icon menu(图标菜单)位于版图编辑窗口左侧,列出了常用命令的图标,将鼠标移动到某一图标上,图标下方就会显示该图标对应的指令。

3、LSW: layer select window(图层选择窗口)。该窗口显示设计版图所用的工艺库文件的位置、可供选择和当前选中的版图图层,以及各图层的图样属性。 如右图显示当前所用工艺库文件位于“MYLIB”目录下,当前选择的图层为“active”。

工艺库文件在工程创建之初已经确定,不用再做操作。而可供选择的图层,根据不同设计需求会有所不同。常用图层名称及其含义工艺库文件在工程创建之初已经确定,不用再做操作。而可供选择的图层,根据不同设计需求会有所不同。常用图层名称及其含义

建立几何图形 1. 矩形(Rectangle) 1)建立矩形命令: Create→Rectangle或快捷键r 或点击图标 2)选取图层

3)画矩形。 (a) 点击左键 (b) 移动鼠标 (c) 点击左键建立矩形 (d) 完成的矩形 (a) (b) (c) (d) 4)按<Esc>键停止画矩形命令。

2.多边形(polygon) (1)方法1 ① 建立多边形命令:Create→polygon或快捷键shift+p 或点击图标。 ② 选取图层。

③ 画多边形。 (a) 点击第一点 (b) 移动鼠标,以此点击各个拐点 (c) 双击或按<Enter>键使多边形封闭 (d) 完成的多边形 (a) (b) (c) (d)

(2)方法2 (a)绘制多个矩形 (b)使用合并命令edit-merge或快捷键shift+m将矩形合并为多边形 (a) (b)

3. 复制(Copy) 1)复制命令Edit→copy,或快捷键c 或点击图标 2)点击目标图形 3)移动鼠标到空白处再次点击完成复制 4) 按<Esc>键停止复制命令

4. 移动(move) 1)复制命令Edit→move,或快捷键m 或点击图标 2)点击目标图形 3)移动鼠标到空白处再次点击完成移动 4) 按<Esc>键停止移动命令

5. 拉伸(stretch) 1)复制命令:Edit→stretch,或快捷键s 或点击图标 2)点击目标图的一条边或一个顶点 3)移动鼠标到空白处再次点击完成拉伸 4) 按<Esc>键停止拉伸命令

6. 标尺(ruler) 1)标尺命令:window→create ruler, 或快捷键k或点击图标 2)点击任意所需一点为起点 3)移动鼠标到空白处再次点击完成标尺 4) 按<Esc>键停止标尺命令 5)按shift+k 清除所有标尺

反相器版图实例 • 在P型衬底上制作CMOS反相器,需要一个PMOS管和一个NMOS管。其中PMOS管制作在N阱中,包含有源扩散区、多晶硅栅;NMOS管包含有源扩散区、多晶硅栅。 • 工艺上为了区分P管、N管,分别添加pselect和nselect两层。 • 为了实现电路功能,必须使用金属层布线,并在金属与半导体之间制作引线孔

衬底连接与布线: • MOS管衬底必须接到相应电位,有源区作为源漏极也需要引线连接。半导体衬底材料必须先制作active有源区,才能通过通孔与金属引线连接。 • 根据不同工艺,通孔尺寸和间距不同。

器件连接关系及端口 : • 用铝线直接连接两管漏极,并可作为输出端; • 多晶硅连接两管栅极,制作通孔后连接金属,作为输入端; • 与金属相连的两管衬底作为power端。

添加端口: • 从LSW 中选择合适的金属层,如metal1。在版图编辑窗口中的菜单栏,选择create—pin。开始为版图添加端口。 • 在“mode”选项后选择rectangle模式,在create shape pin 窗口编辑输入输出端口。

可以在create shape pin窗口中选择“sym pin”切换至create symbolic pin窗口。

编辑好端口属性后,在版图编辑窗口中需要添加端口的位置画一小矩形,之后再单击一次,放置端口名,即完成一个端口。编辑好端口属性后,在版图编辑窗口中需要添加端口的位置画一小矩形,之后再单击一次,放置端口名,即完成一个端口。 • 这里的metal1端口图层仅表示连线关系,不生成掩模板,无所谓规则,只要与实际版图上的铝线连接即可。

添加power端口需要选择sym pin模式,打开create symbolic pin 窗口。 • 以添加vdd端口为例, • 端口名应为“vdd!”, • I/O type 选为“jumper”, • pin type 选择“metal1”。

可以在create symbolic pin窗口中选择“shape pin”切换至create shape pin窗口。

三、版图验证与检查 • 版图验证是指采用专门的软件工具,对版图进行若干项目的验证。例如: • 是否符合设计规则? • 版图和电路图是否一致? • 版图是否存在短路、断路及悬空的节点?

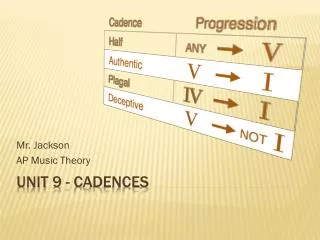

版图验证项目包括五项: • (1) DRC (Design Rule Check) 设计规则检查。 • (2) ERC(Electrical Rule Check) 电学规则检查。 • (3) LVS(Layout Versus Schemati) 版图和电路图一致性比较 • (4) LPE(Layout Parameter Extruction) 版图寄生参数提取 • (5) PRE(Parasitic Resistance Extruction) 寄生电阻提取 • 其中,DRC和LVS是必做的验证。

1、 DRC • Design rule checking (设计规则检查)。版图的设计必须根据DRC 规则文件进行,不同工艺的DRC 规则文件不同。 • 建议完成一部分设计之后就做一次,分阶段进行。避免完成全图后再做DRC,错误之间相互牵连不便修改。 • DIVA 下的DRC 规则文件名为divaDRC.rul。通常与工艺库文件存放在相同目录。 • 在版图编辑窗口,单击菜单verify ——DRC,弹出DRC 规则检查对话框,

点击OK,开始DRC,可以在CIW 窗口看到运行信息。如果有错,CIW窗口会提示错误数量及错误类型,并在版图编辑窗口出现闪烁标记。

2 1 3

1 Active must be inside select

2 Gate enclosure of active: 0.30um

3 Active enclosure of gate: 0.45um

可以选择Verify-Markers-Find菜单帮助找错。单击菜单后会弹出一个窗口,在这个窗口中单击apply就可以显示第一个错误。可以选择Verify-Markers-Find菜单帮助找错。单击菜单后会弹出一个窗口,在这个窗口中单击apply就可以显示第一个错误。 • 如果选中“zoom to markers”,则会在版图编辑窗口中,将错误图形的位置居中放置。

2、 Extractor • 版图提取,提取版图网表信息,用于与电路网表对照验证。 • 在版图编辑窗口菜单中选择verify-extract 即可打开对话框。

提取成功后,在版图文件的存放目录下,增加一个extracted文件。打开可以看到提取出来的器件和端口。提取成功后,在版图文件的存放目录下,增加一个extracted文件。打开可以看到提取出来的器件和端口。 • 选择Verify-probe菜单,在弹出窗口中可以选择查看连接关系。

3、 LVS • Layout vs. schematic comparison(版图与电路对比),检查设计完成的版图是否与原电路相符。 • 在版图编辑窗口菜单中选择verify-LVS 即可打开对话框。

注意:如果之前运行过LVS,此时会出现一个提示窗口。选中form contents(重新创建LVS文件内容) ,继续LVS。

错误位置 错误类型 • LVS验证报告: 错误原因 错误数量