Bus

Bus. MCS51. MCS51 External R/W Operation. MCS51 Programme Memory Access. Parallel Port Pin Description. ECP mode Forward. ECP mode Reverse. Parallel Port IPC block. PCI Bus Pin List. Initiator Target. PCI Commands. Command Type C/BE[3:0]#

Bus

E N D

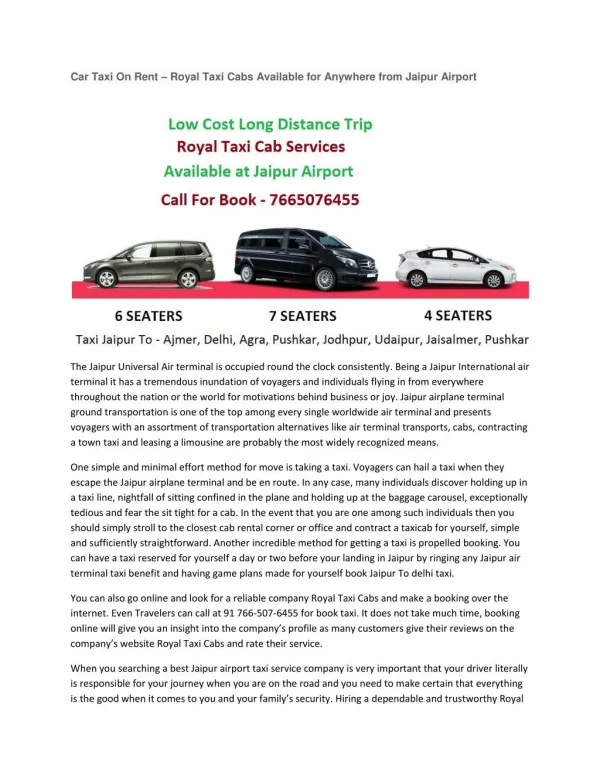

Presentation Transcript

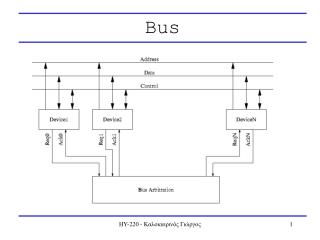

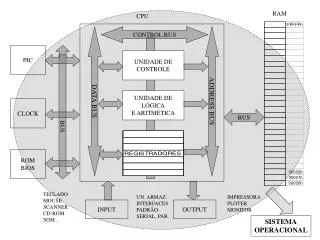

Bus ΗΥ-220 - Καλοκαιρινός Γιώργος

MCS51 ΗΥ-220 - Καλοκαιρινός Γιώργος

MCS51 External R/W Operation ΗΥ-220 - Καλοκαιρινός Γιώργος

MCS51 Programme Memory Access ΗΥ-220 - Καλοκαιρινός Γιώργος

Parallel Port Pin Description ΗΥ-220 - Καλοκαιρινός Γιώργος

ECP mode Forward ΗΥ-220 - Καλοκαιρινός Γιώργος

ECP mode Reverse ΗΥ-220 - Καλοκαιρινός Γιώργος

Parallel Port IPC block ΗΥ-220 - Καλοκαιρινός Γιώργος

PCI Bus Pin List ΗΥ-220 - Καλοκαιρινός Γιώργος

Initiator Target ΗΥ-220 - Καλοκαιρινός Γιώργος

PCI Commands Command Type C/BE[3:0]# • Interrupt Acknowledge 0000 • Special Cycle 0001 • I/O Read 0010 • I/O Write 0011 • Memory Read 0110 • Memory Write 0111 • Configuration Read 1010 • Configuration Write 1011 • Memory Read Multiple 1100 • Dual Address Cycle 1101 • Memory Read Line 1110 • Memory Write and Invalidate 1100 ΗΥ-220 - Καλοκαιρινός Γιώργος

Basic Read Operation ΗΥ-220 - Καλοκαιρινός Γιώργος

Basic Write Operation ΗΥ-220 - Καλοκαιρινός Γιώργος

Basic Arbitration ΗΥ-220 - Καλοκαιρινός Γιώργος

Master Initiated Termination • Completion : The master has concluded its intended transaction. • Timeout : Termination when the master’s GNT#_ is deasserted and its internal Latency Timer has expired. ΗΥ-220 - Καλοκαιρινός Γιώργος

Master Abort Termination ΗΥ-220 - Καλοκαιρινός Γιώργος

Master Initiated Termination ΗΥ-220 - Καλοκαιρινός Γιώργος

Target Initiated Termination • Retry : Termination requested before any data is tranferred. • Disconnect : Termination requested with or after data was transferred on the initial phase because the target is unable to respond within the target subsequent latency requirement, and is temporarily unable continue bursting. • Target Abort : Adnormal termination requested because the target detected a fatal error or the target will never be able to complete the request. ΗΥ-220 - Καλοκαιρινός Γιώργος

Target Initiated Termination Signaling Rules 1/2 • A data phase completes on the rising edge on which IRDY# is asserted and either STOP# or TRDY# is asserted. • Independent of the state of STOP#,a data transfer takes place on every rising edge of clock where both IRDY# and TRDY# are asserted. • Once the target asserts STOP#, it must keep STOP# asserted until FRAME# is deasserted, whereupon it must deassert STOP#. ΗΥ-220 - Καλοκαιρινός Γιώργος

Target Initiated Termination Signaling Rules 2/2 • Once a target has asserted TRDY# or STOP#, it cannot change DEVSEL#, TRDY# or STOP# until the current data phase completes. • Whenever STOP# is asseted, the master must deassert FRAME# as soon as IRDY# can be asserted. • If not already deasserted, TRDY#, STOP#, and DEVSEL# must be deasserted the clock following the completion of the last data phase and must be tri-stated the next clock. ΗΥ-220 - Καλοκαιρινός Γιώργος

Target Initiated Termination 1/2 ΗΥ-220 - Καλοκαιρινός Γιώργος

Target Initiated Termination 2/2 ΗΥ-220 - Καλοκαιρινός Γιώργος

Disconnect-1 Without Data Termination ΗΥ-220 - Καλοκαιρινός Γιώργος

Disconnect-2 Without Data Termination ΗΥ-220 - Καλοκαιρινός Γιώργος

Retry ΗΥ-220 - Καλοκαιρινός Γιώργος

PCI Configuration Header ΗΥ-220 - Καλοκαιρινός Γιώργος

Status Register Bit Assignmet ΗΥ-220 - Καλοκαιρινός Γιώργος

Command Register Bit Assignmet ΗΥ-220 - Καλοκαιρινός Γιώργος

Base Address Register Format ΗΥ-220 - Καλοκαιρινός Γιώργος