Mobility Enhancement in Strained Silicon-Germanium Channels: Collaborative Workshop Insights

E N D

Presentation Transcript

SiNANO Workshop David LeadleyUniversity of Warwick Carrier mobility enhancement in strained silicon germanium channels

Collaborators • Warwick Tim Grasby, Andy Dobbie, Chris Beer, Jon Parsons, Evan Parker, Terry Whall • IMEC Gareth Nicholas, Marc Meuris, M Heyns, P Zimmerman, Matty Caymax, ++ • SINANO partners KTH,Udine, Chalmers, AMO

Why is mobility still critical ? High mobility - light mass and minimal scattering • ITRS – long term years • By 2020, Lg=5nm, Vdd=0.7V • Mobility enhancement factor of 1.04 each node • Ballistic enhancement factor x2 • Double gate structures – light doping

Why add Ge? • ADVANTAGES • Smaller bandgap • Lighter hole mass • Strain – splits bands and reduces scattering • BUT… • Native oxide no good • Band-to-band tunnelling

Pseudomorphic Si0.64Ge0.36 on Si Mobility doubled

Impact Ionisation Reduced impact ionisation for SiGe, despite higher mobility Nicholas et al, Electronics Letters41, 20052074

Metal HfO2 SiO2 SiGe Si High-k gated SiGe • Deposited HfO2 • Si cap – oxidises to thin SiO2 interlayer Lowest EOT 12Å < 1nm

Metal gate/HfO2 gate stack development for Si(cap)/Si0.8Ge0.2 channel Interface state density (W gate) Gate leakage Warwick, AMO, Chalmers

High-k/metal gated Si0.8Ge0.2 surface p-channel devices ........enhancements beating Intel (IEDM 2004) KTH, Warwick, Chalmers, AMO

Effective Mobility Best SiGe (25%) devices show mobility enhancement over silicon control Mobility degradation compared to universal – interface roughness and Coulomb scattering important KTH, Warwick, Chalmers, AMO

[001] [011] [110] [011] (110) substrate (100) substrate HOT SiGe • Hybrid Orientation Technology • n on (100), p on (110) in Si, Yang et al. IEDM 2003 • in Si, no variation with orientation for long channels, but <110> best for short channels, Saito et al VLSI 2006 • 50% enhanced Idsat for SiGe (110) over Si (100),3.3x for mobility, Liu et al VLSI 2006

= 3.2 nm Novel p-channel/substrate orientations … enhancement beating Liu et al(VLSI Symp 2006) KTH, Warwick, Chalmers, AMO

Unstrained Ge pMOS • High performance Ge pMOS devices using a Si-compatible process flow • Zimmerman et al. IEDM 2006 4nm HfO2 2μm Ge on Si substrate 12Å EOT, TDD 107-108 cm-2 PMOS fabricated with Lg ~125 nm IMEC

Unstrained Ge Ge + anneal Si IMEC

Nit spread 0.2-8x1012cm-2 • affects Ids, gm and Vt Uniformity restored after anneal IMEC

Thinner EOT? Si Starts to leak when too thin ! • Mobility increase with thinner HfO2 • less charge trapping • Ragnarsson et al. IEEE TED 53, 1657 ( 2006) IMEC

Mobility in unstrained Ge μ > 300 cm2/Vs Correction required for Rsd in short channel devices Lg<0.25μm IMEC

Investigating trapped charge Dit varies across wafer 1011 - 2x1012cm-2 Warwick, IMEC

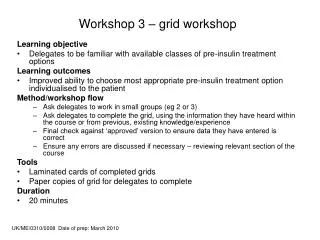

Extract Dit in 3 ways at 300K: • from Vt – average all energies • subthreshold slope – specific energy • charge pumping Interface charge density Warwick, IMEC

Mobility modelling at 4K • At low T, with confinement only have one HH subband. Fit using ni and D as parameters ... Warwick, IMEC

As grown Annealed Modelled 4K mobility ni agrees with values from Dit Δdecreases after anneal from 0.6nm to 0.5nm,hence μSR increases by 35% μ300Kmust also depend on surface roughness Warwick, IMEC

Strain tuning buffers • Strained-Si by local strain now in production • Si1-yGey virtual substrates for global strain • y~0.2 for s-Si • y~0.5 for s-Si1-xGex • y~0.8 for s-Ge • Need low TDD and zero pile-up

Terrace Graded VS – better than industrial quality 20% Ge TDD ≤ 105cm-2, PUD=0 XTEM 10x10um2 AFM image indicating RMS roughness 1.5nm Warwick, LETI, Jeulich

State-of-the-art sSi electron mobilityfrom TG-VSs y = 15 -27% strain 0.6 – 1.1% State of the art Warwick, Udine, KTH F. Driussi et al., ULIS 2007

sGe global platform- 80% terrace grade TDD=3x105/cm-2, PUD = 0, RMS ≈ 8nm Warwick, FZ-Jeulich, LETI

Strained Si Strained Ge 300nm Si0.2Ge0.8 Grade Seed layer Si Sub Novel thin VS for sGe 20x20 um2 AFM image. 1.3nm RMS, fully relaxed 80% platform TDD ≈ 106/cm2 range Warwick

150nm TiN 4nm ALD HfO2 Positive Vt due to gate workfunction Strained Ge pMOS ASM, Warwick, IMEC

Record Ge mobility via CMOS process Peak μ = 650 cm2/Vs Warwick, IMEC G. Nicholas et al., IEEE EDL 28, 825 (2007)

Further comments on s-Ge • Full band Monte Carlo calculations, incl. BTBT, SCE etc. show best prospect for pMOS … • … strained-Ge directly on Si ! Krishnamohan et al (Stanford) VLSI (2006) • For s-SiGe OI, Idsat enhancement in short channels exceeds μ increase in long channel.Tsutomu Tezuka et al. VLSI (2006) • nMOS still a problem for Ge …… but tensile strain Si0.1Ge0.9 on relaxed Ge promising.

Summary • Addition of Ge improves mobility • High-k makes Ge viable • Mobility enhancements relevant for nanometre scale devices

30% TDD ≈ 4 x 104 cm-2 PUD = 0 Terrace grading – new generation of virtual substrates Warwick

LG 30% ≈105 cm-2 TDD Pile-up ≈1 cm-1

High stability sSi layers Linear Grading Relaxation (%) Terrace Grading Strained Si thickness (nm) Warwick, FZ-Jeulich J. Parsons et al., ULIS 2007

Extended Stacking Faults PVTEM image of 180nm strained silicon layer Defect etch image of 20nm strained silicon layer Warwick, FZ-Jeulich J. Parsons et al., ULIS 2007

Extended Stacking Faults “Perfect” dislocation Stacking fault Trailing (30°) “partial” dislocation Leading (90°) “Partial” dislocation S-Si SiGe

Stacking faults– effective misfit dislocation blockers? Defect etch images of 30nm strained silicon layer Warwick, FZ-Jeulich J. Parsons et al., ULIS 2007

50% terrace graded (for sSi) TDD = 2x105 cm-2 PUD = 0 Warwick

≈ 20% TG - slower growth(+sSi) TDD = 4 x 104/cm2 PUD = 0

Schottky Barrier MOSFET- world best? Tunnelling f(m*) Thermionic emmision Measurement Modelling UCL, Warwick, Glasgow D.J. Pearman et al., IEEE Trans ED (accepted 2006)