NIOS 1.1

TM. NIOS 1.1. Simulation Flow A Step by Step guidelines for both VHDL & Verilog. Directory Organisation. DB1. DB2. DB3. NIOS VHDL Design Flow. NIOS Megawizard. DB1. Software Writing. Update PTF File. Add DO_BUILD_SIM ="1". DB2. NIOS-BUILD. DB2. Generate_Project. NIOS-BUILD.

NIOS 1.1

E N D

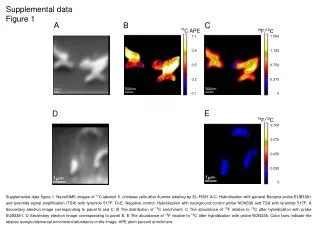

Presentation Transcript

TM NIOS 1.1 Simulation Flow A Step by Step guidelines forboth VHDL & Verilog

Directory Organisation DB1 DB2 DB3

NIOS VHDL Design Flow NIOS Megawizard DB1 Software Writing Update PTF File Add DO_BUILD_SIM ="1" DB2 NIOS-BUILD DB2 Generate_Project NIOS-BUILD Simulation ? *.do files writing DB1 DB3 VHDL_simulation DB3 QuartusCompilation ModelSimSimulation QuartusProgrammer Result Software Modification Requirements Meet Hardware Modification NIOS-RUN

Environment prerequisites • Nios 1.1 must be installed • Copy following files • generate_project • vhdl_simulation • trace2obj in C:\Cygwin\usr\altera\excalibur\nios-sdk\bin

Summary of the tutorial • Generating a Nios System Variation • Compiling Your Software • Modifying the PTF File • Generating the Simulation Environment • Preparing a Modelsim Script • Simulating with Modelsim • Tracing Processor’s Activity • Generating an EDIF Netlist & Compiling w/ Quartus II • Notes

Generating a Nios System Variation • Open Quartus and Create a New Project • Working Directory: Nios_project • Project Name & Top Level Name: mycpu • Launch the MegaWizard Plug-In manager • Create a New Custom Variation of Nios • Give it the name: mycpu • Select ALTERA Excalibur NIOSTM megafunctions • Select Verilog HDL output type • Do parameterise your core system, for instance • NIOS 32bits, 16bits @, 256 files reg., 3bits shifter, No MSTEP, No MUL • Rom_prg, 4K 32bits @= 0x0000, leave blank the contents • Ram_sys, 1K 32bits @= 0x1000 • Timer @= 0x2000, #IRQ= 20 • Led_pio, 4 outputs @= 0x3000 • Main Program Memory = rom_prg • Main Data Memory = ram_sys • Boot Device = rom_prg • Int. Vector table loc. = ram_sys • Synthesis Target = None "mycpu.ptf" file is generated which describes your whole NIOS system

Compiling Your Software Application • Create Your C Code (for example, mycode.c) in C:\NIOS_project\mycpu_sdk\src • Open a Bash Window & Go in C:\NIOS_project\mycpu_sdk\src • Run NIOS-BUILDTo Generate Compiled Code • mycode.srec • mycode.objdump

Modifying the PTF file • Open mycpu.ptf file with vi (or Your Favorite Editor) in C:\Nios_project • Turn On Simulation Support File Generation by Setting Variable do_build_sim to 1 As Follows: SYSTEM mycpu { WIZARD_SCRIPT_ARGUMENTS { do_build_sim = "1" ; • Rom_prg user file specification • Find the MODULE rom_prg section and Change the following lines WIZARD_SCRIPT_ARGUMENTS { Writeable = "0"; Contents = "user_file"; Initfile = "mycpu_sdk\\src\\mycode.srec"; }

Generating the Simulation Environment Skip this step if you run a verilog simulation • Open BASH window and go in c:\NIOS_project\ • Run the following command • GENERATE_PROJECT mycpu Only verilog files are generated at this point. • VHDL files generation • Go inc:\NIOS_project\mycpu_sim • Run VHDL_SIMULATION mycpu_test_bench.v > compile_vhdl.do

Preparing a ModelSim Script Compile_vhdl.do cd C:/NIOS_project/mycpu_sim vcom -work work ./nios_cpu_dr.vhd vcom -work work ./nios_cpu_ar.vhd vcom -work work ./nios_cpu_cr.vhd vcom -work work ./nios_cpu_register_ram.vhd vcom -work work ./nios_cpu_major_opcode_table.vhd vcom -work work ./nios_cpu_subtable_w.vhd vcom -work work ./nios_cpu_instruction_decoder.vhd vcom -work work ./nios_cpu_cpu_core.vhd vcom -work work ./timer.vhd vcom -work work ./led_pio.vhd vcom -work work ./rom_prg.vhd vcom -work work ./ram_sys_lane_0.vhd vcom -work work ./ram_sys_lane_1.vhd vcom -work work ./ram_sys_lane_2.vhd vcom -work work ./ram_sys_lane_3.vhd vcom -work work ./ram_system.vhd vcom -work work ./nios_rg.vhd vcom -work work ./nios_pbm.vhd vcom -work work ./nios_core.vhd vcom -work work ./test_equipment.vhd vcom -work work ./mycpu_test_bench.vhd Vsim work.mycpu_test_bench • VHDL Edit the compile_vhdl.dofile • Remove the initial header lines, leaving only the file names • Add vcom -work workfor each line • Re-Order memory files included Memory Lanes have to be declared before thememory top level definition • Add vsim work.mycpu_test_bench You should get the following macro file • Verilog Create acompile_verilog.do • Add vlog -work work ./mycpu_test_bench.v • Add vsim work.mycpu_test_bench

Simulating with ModelSim 1/2 Skip this step if you run a verilog simulation • Launch Modelsim Altera-Edition or SE 5.4 • Open "FileChange directory…" menu and select C:/NIOS_project/mycpu_sim • Open the "OptionsCompiler…" menu • Disable "Check for Vital Compliance" • Disable "Optimize for Vital" • Enable "Use 1993 Language Syntax" • Type do compile_vhd ordo compile_verilog.doin the command line • Open the "ViewStructure" menu • Open the "ViewSignal" menu

Simulating with ModelSim 2/2 • Select the following signals: • /mycpu_test_bench/the_mycpu_core/clk • /mycpu_test_bench/the_mycpu_core/reset_n • /mycpu_test_bench/the_mycpu_core/the_mycpu_cpu/irq_number • /mycpu_test_bench/the_mycpu_core/the_mycpu_cpu/ifetch • /mycpu_test_bench/the_mycpu_core/the_mycpu_cpu/mem_addr [set the radix format to hex] • /mycpu_test_bench/the_mycpu_core/the_mycpu_cpu/data_from_cpu[set the radix format to hex] • /mycpu_test_bench/the_mycpu_core/the_mycpu_cpu/data_to_cpu[set the radix format to hex] • In the Waves window, open "EditDisplay Properties…" • Set to 1 the Signal Names path elements displayed • In the Waves window, Save your waves format as wave.do • Open the "OptionsSimulation..." menu and enable "Suppress Warning" for both Synopsys and IEEE packages. • Type "run 200µs" in the command line

Tracing Processor’s Activity 1/3 The goal is to dump the processor’s activity using assembly code • Restart the simulation by typing restart -f • Open the "Viewlist" window • In the Waves window, select & slide to the List window the following signals • /mycpu_test_bench/the_mycpu_core/the_mycpu_cpu/mem_addr(must be first in the list) • /mycpu_test_bench/the_mycpu_core/the_mycpu_cpu/ifetch • Under the List window, open the "PropDisplay Props…" menu and set Signal Names = 1 for path elements displayed. • Set the mem_addr signal radix in the list window to Hexadecimal • Select the signal and open "Prop Signal Props…" and select Hexadecimal • Change width characters displayed to 15. • Rerun the simulation as long as you want (200µs)

Tracing Processor’s Activity 2/3 • Under the List window, open the "PropDisplay Props…" menu and select the Triggers Tab. • Enable the Trigger Gating and fill the Expression area by: • /mycpu_test_bench/the_mycpu_core/the_mycpu_cpu/ifetch = 1 • Open "FileWrite List (Tabular)" menu and save it as mycode.lst • Save your list format as list.do • Create a Debug directory in the top working directory c:\NIOS_project\ • Move mycode.lst and mycode.objdumpThe latter is locatedc:\NIOS_project\mycpu_sdk\src directory • Open BASH Window and go under c:\NIOS_project\debug and type • Trace2obj mycode.objdump mycode.lst It will build the mycode.lst-objdump file which represents the processor activity for your simulation.

Tracing Processor’s Activity 3/2 TRACE2OBJ mycode.srec mycode.lst NIOS-BUILD mycode.c mycode.objdump

Generating an EDIF & Compiling w/ Quartus II • Edit file mycpu.ptf in c:\NIOS_project\ • Enable the synthesis by putting skip_synth option to 0 • Open BASH window and go under c:\NIOS_project\ • In the Bash Window, run the following command • GENERATE_PROJECT mycpu • In Quartus II, use the generated EDIF in your project

Notes • Simulating Once the SW Has Been Modified • Step 4 • Type restart –f under Modelsim command line • Type do compile_all.do(or compile_verilog.do) • Type wave.do • Type list.do