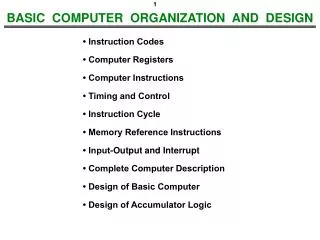

Basic Computer Organization

E N D

Presentation Transcript

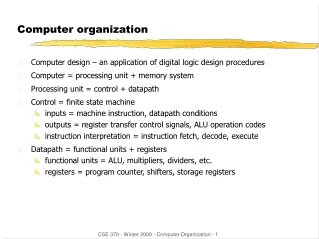

Basic Computer Organization Chapter 2 S. Dandamudi

Basic components The processor Execution cycle System clock Number of addresses 3-address machines 2-address machines 1-address machines 0-address machines Load/store architecture Flow control Branching Procedure calls Memory Basic operations Types of memory Storing multibyte data Input/Output Performance: Data alignment Outline S. Dandamudi

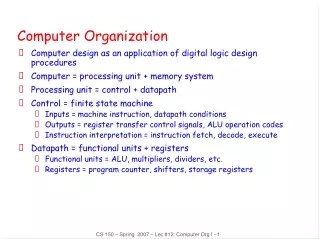

Basic Components • Basic components of a computer system • Processor • Memory • I/O • System bus • Address bus • Data bus • Control bus S. Dandamudi

Basic Components (cont’d) S. Dandamudi

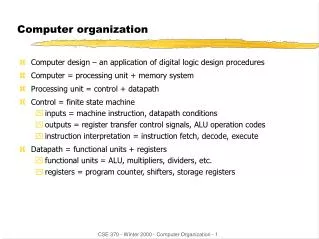

The Processor • Processor can be thought of executing • Fetch-decode-execute cycle forever • Fetch an instruction from the memory • Decode the instruction • Find out what the operation is • Execute the instruction • Perform the specified operation S. Dandamudi

The Processor (cont’d) • System clock • Provides timing signal • Clock period = 1 Clock frequency S. Dandamudi

Number of Addresses • Four categories • 3-address machines • 2 for the source operands and one for the result • 2-address machines • One address doubles as source and result • 1-address machine • Accumulator machines • Accumulator is used for one source and result • 0-address machines • Stack machines • Operands are taken from the stack • Result goes onto the stack S. Dandamudi

Number of Addresses (cont’d) • Three-address machines • Two for the source operands, one for the result • RISC processors use three addresses • Sample instructions add dest,src1,src2 ; M(dest)=[src1]+[src2] sub dest,src1,src2 ; M(dest)=[src1]-[src2] mult dest,src1,src2 ; M(dest)=[src1]*[src2] S. Dandamudi

Number of Addresses (cont’d) • Example • C statement A = B + C * D – E + F + A • Equivalent code: mult T,C,D ;T = C*D add T,T,B ;T = B+C*D sub T,T,E ;T = B+C*D-E add T,T,F ;T = B+C*D-E+F add A,T,A ;A = B+C*D-E+F+A S. Dandamudi

Number of Addresses (cont’d) • Two-address machines • One address doubles (for source operand & result) • Last example makes a case for it • Address T is used twice • Sample instructions load dest,src; M(dest)=[src] add dest,src; M(dest)=[dest]+[src] sub dest,src; M(dest)=[dest]-[src] mult dest,src; M(dest)=[dest]*[src] S. Dandamudi

Number of Addresses (cont’d) • Example • C statement A = B + C * D – E + F + A • Equivalent code: load T,C ;T = C mult T,D ;T = C*D add T,B ;T = B+C*D sub T,E ;T = B+C*D-E add T,F ;T = B+C*D-E+F add A,T ;A = B+C*D-E+F+A S. Dandamudi

Number of Addresses (cont’d) • One-address machines • Uses special set of registers called accumulators • Specify one source operand & receive the result • Called accumulator machines • Sample instructions load addr; accum = [addr] store addr; M[addr] = accum add addr; accum = accum + [addr] sub addr; accum = accum - [addr] mult addr; accum = accum * [addr] S. Dandamudi

Number of Addresses (cont’d) • Example • C statement A = B + C * D – E + F + A • Equivalent code: load C ;load C into accum mult D ;accum = C*D add B ;accum = C*D+B sub E ;accum = B+C*D-E add F ;accum = B+C*D-E+F add A ;accum = B+C*D-E+F+A store A ;store accum contents in A S. Dandamudi

Number of Addresses (cont’d) • Zero-address machines • Stack supplies operands and receives the result • Special instructions to load and store use an address • Called stack machines (Ex: HP3000, Burroughs B5500) • Sample instructions push addr; push([addr]) pop addr; pop([addr]) add; push(pop + pop) sub; push(pop - pop) mult; push(pop * pop) S. Dandamudi

Number of Addresses (cont’d) • Example • C statement A = B + C * D – E + F + A • Equivalent code: push E sub push C push F push D add Mult push A push B add add pop A S. Dandamudi

Load/Store Architecture • Instructions expect operands in internal processor registers • Special LOAD and STORE instructions move data between registers and memory • RISC and vector processors use this architecture • Reduces instruction length S. Dandamudi

Load/Store Architecture (cont’d) • Sample instructions load Rd,addr;Rd = [addr] store addr,Rs;(addr) = Rs add Rd,Rs1,Rs2;Rd = Rs1 + Rs2 sub Rd,Rs1,Rs2;Rd = Rs1 - Rs2 mult Rd,Rs1,Rs2;Rd = Rs1 * Rs2 S. Dandamudi

Number of Addresses (cont’d) • Example • C statement A = B + C * D – E + F + A • Equivalent code: load R1,B mult R2,R2,R3 load R2,C add R2,R2,R1 load R3,D sub R2,R2,R4 load R4,E add R2,R2,R5 load R5,F add R2,R2,R6 load R6,A store A,R2 S. Dandamudi

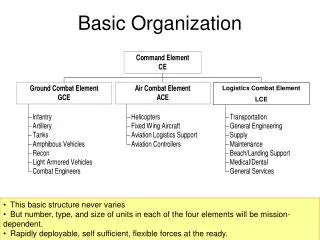

Flow of Control • Default is sequential flow • Several instructions alter this default execution • Branches • Unconditional • Conditional • Procedure calls • Parameter passing • Register-based • Stack-based S. Dandamudi

Flow of Control (cont’d) • Branches • Unconditional branch target • Absolute address • PC-relative • Target address is specified relative to PC contents • Example: MIPS • Absolute address j target • PC-relative b target S. Dandamudi

Flow of Control (cont’d) S. Dandamudi

Flow of Control (cont’d) • Branches • Conditional • Jump is taken only if the condition is met • Two types • Set-Then-Jump • Condition testing is separated from branching • Condition code registers are used to convey the condition test result • Example: Pentium code cmp AX,BX je target S. Dandamudi

Flow of Control (cont’d) • Test-and-Jump • Single instruction performs condition testing and branching • Example: MIPS instruction beq Rsrc1,Rsrc2,target • Jumps to target if Rsrc1 = Rsrc2 S. Dandamudi

Flow of Control (cont’d) • Procedure calls • Requires two pieces of information to return • End of procedure • Pentium • uses ret instruction • MIPS • uses jr instruction • Return address • In a (special) register • MIPS allows any general-purpose register • On the stack • Pentium S. Dandamudi

Flow of Control (cont’d) S. Dandamudi

Flow of Control (cont’d) • Parameter passing • Register-based • Internal registers are used • Faster • Limit the number of parameters • Due to limited number of available registers • Stack-based • Stack is used • Slower • Requires memory access • General-purpose • Not limited by the number of registers S. Dandamudi

Memory can be viewed as an ordered sequence of bytes Each byte of memory has an address Memory address is essentially the sequence number of the byte Such memories are called byte addressable Number of address lines determine the memory address space of a processor Memory S. Dandamudi

Memory (cont’d) • Two basic memory operations • Read operation (read from memory) • Write operation (write into memory) • Access time • Time needed to retrieve data at addressed location • Cycle time • Minimum time between successive operations S. Dandamudi

Memory (cont’d) • Steps in a typical read cycle • Place the address of the location to be read on the address bus • Activate the memory read control signal on the control bus • Wait for the memory to retrieve the data from the addressed memory location • Read the data from the data bus • Drop the memory read control signal to terminate the read cycle • A simple Pentium memory read cycle takes 3 clocks • Steps 1&2 and 4&5 are done in one clock cycle each • For slower memories, wait cycles will have to be inserted S. Dandamudi

Memory (cont’d) • Steps in a typical write cycle • Place the address of the location to be written on the address bus • Place the data to be written on the data bus • Activate the memory write control signal on the control bus • Wait for the memory to store the data at the addressed location • Drop the memory write control signal to terminate the write cycle • A simple Pentium memory write cycle takes 3 clocks • Steps 1&3 and 4&5 are done in one clock cycle each • For slower memories, wait cycles will have to be inserted S. Dandamudi

Memory (cont’d) • Some properties of memory • Random access • Accessing any memory location takes the same amount of time • Volatility • Volatile memory • Needs power to retain the contents • Non-volatile memory • Retains contents even in the absence of power • Basic types of memory • Read-only memory (ROM) • Read/write memory (RAM) S. Dandamudi

Memory (cont’d) • Read-only memory (ROM) • Cannot be written into this type of memory • Non-volatile memory • Most are factory programmed (i.e., written) • Programmable ROMs (PROMs) • Can be written once by user • A fuse is associated with each bit cell • Special equipment is needed to write (to blow the fuse) • PROMS are useful • During prototype development • If the required quantity is small • Does not justify the cost of factory programmed ROM S. Dandamudi

Memory (cont’d) • Erasable PROMs (EPROMs) • Can be written several times • Offers further flexibility during system prototyping • Can be erased by exposing to ultraviolet light • Cannot erase contents of selected locations • All contents are lost • Electrically erasable PROMs (EEPROMs) • Contents are electrically erased • No need to erase all contents • Typically a subset of the locations are erased as a group • Most EEPROMs do not provide the capability to individually erase contents of a single location S. Dandamudi

Memory (cont’d) • Read/write memory • Commonly referred to as random access memory (RAM) • Volatile memories • Two basic types • Static RAM (SRAM) • Retains data with no further maintenance • Typically used for CPU registers and cache memory • Dynamic RAM (DRAM) • A tiny capacitor is used to store a bit • Due to leakage of charge, DRAMs must be refreshed to retain contents • Read operation is destructive in DRAMs S. Dandamudi

Memory (cont’d) • DRAM types • FPM DRAMs • FPM = Fast Page Mode • EDO DRAMs • EDO = Extended Data Out • Uses pipelining to speedup access • SDRAMs • Use an external clock to synchronize data output • Also called SDR SDRAMs (Single Data Rate) • DDR SDRAMs • DDR = Double Data Rate • Provides data on both falling and rising edges of the clock • RDRAMs • Rambus DRAM S. Dandamudi

Storing Multibyte Data S. Dandamudi

Storing Multibyte Data (cont’d) • Little endian • Used by Intel IA-32 processors • Big endian • Used most processors by default • MIPS supports both byte orderings • Big endian is the default • Not a problem when working with same type of machines • Need to convert the format if working with a different machine • Pentium provides two instructions for conversion • xchg for 16-bit data • bswap for 32-bit data S. Dandamudi

Input/Output • I/O controller provides the necessary interface to I/O devices • Takes care of low-level, device-dependent details • Provides necessary electrical signal interface S. Dandamudi

Input/Output (cont’d) • Processor and I/O interface points for exchanging data are called I/O ports • Two ways of mapping I/O ports • Memory-mapped I/O • I/O ports are mapped to the memory address space • Reading/writing I/O is similar to reading/writing memory • Can use memory read/write instructions • Motorola 68000 uses memory-mapped I/O • Isolated I/O • Separate I/O address space • Requires special I/O instructions (like in and out in Pentium) • Intel 80x86 processors support isolated I/O S. Dandamudi

Input/Output (cont’d) • Pentium I/O address space • Provides 64 KB I/O address space • Can be used for 8-, 16-, and 32-bit I/O ports • Combination cannot exceed the total I/O address space • can have 64 K 8-bit ports • can have 32 K 16-bit ports • can have 16 K 32-bit ports • A combination of these for a total of 64 KB • I/O instructions do not go through segmentation or paging • I/O address refers to the physical I/O address S. Dandamudi

Performance: Data Alignment S. Dandamudi

Performance: Data Alignment (cont’d) Unaligned Aligned S. Dandamudi

Performance: Data Alignment (cont’d) • Data alignment • Soft alignment • Data is not required to be aligned • Data alignment is optional • Aligned data gives better performance • Used in Intel IA-32 processors • Hard alignment • Data must be aligned • Used in Motorola 680X0 and Intel i860 processors S. Dandamudi

Performance: Data Alignment (cont’d) • Data alignment requirements for byte addressable memories • 1-byte data • Always aligned • 2-byte data • Aligned if the data is stored at an even address (i.e., at an address that is a multiple of 2) • 4-byte data • Aligned if the data is stored at an address that is a multiple of 4 • 8-byte data • Aligned if the data is stored at an address that is a multiple of 8 Last slide S. Dandamudi