CPU, Programmausführung

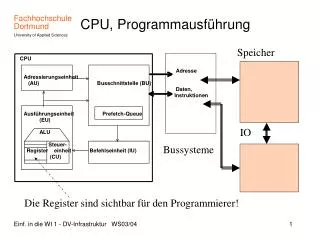

CPU, Programmausführung. Speicher. IO. Bussysteme. Die Register sind sichtbar für den Programmierer!. CPU, Programmausführung. Ausführungseinheit:

CPU, Programmausführung

E N D

Presentation Transcript

CPU, Programmausführung Speicher IO Bussysteme Die Register sind sichtbar für den Programmierer! Einf. in die WI 1 - DV-Infrastruktur WS03/04

CPU, Programmausführung • Ausführungseinheit: • Gesteuert durch die in der Befehlseinheit stehenden Maschineninstruktion werden Daten verarbeitet. Die Daten sind entweder in den Registern vorhanden oder werden aus dem Speicher bzw. der IO geholt. • Daneben gibt es Transportinstruktionen, die Daten aus dem Speicher in Register holen oder aus Registern abspeichern (bzw. IO). Einf. in die WI 1 - DV-Infrastruktur WS03/04

CPU, Programmausführung • Die Adressiereinheit sorgt dafür, dass die richtigen Adressen an die Speichersteu-erung gegeben werden. • Die Busschnittstelle sorgt für die Kommuni-kation mit der „Außenwelt“ der CPU. • Sie enthält die „Prefetch-Queue“. Dort werden Instruktionen auf Vorrat gelesen, während parallel die Verarbeitung von CPU-Daten läuft. Einf. in die WI 1 - DV-Infrastruktur WS03/04

CPU • Befehlszyklus der CPU: • while (TRUE) { • Hole nächste Instruktion (Adresse im IP); • Führe Instruktion aus; • if (Interrupt) Führe Interruptmechanismus aus; • } Einf. in die WI 1 - DV-Infrastruktur WS03/04

Register mov-Instruktion: kopieren zwischen Registern, vom Register zum Speicher, vom Speicher zum Register mov ist die am häufigsten vorkommende Instruktion im Programmtext Einf. in die WI 1 - DV-Infrastruktur WS03/04

Vom Programm zur Machineninstruktion • Ein kleines Beispielprogramm in C++ • int a, b, c; • int main (void) { • a=2; • b=8; • c=a+b; • if (c>=0) c=-3*c; • else c=2*c; • return 0; • } Einf. in die WI 1 - DV-Infrastruktur WS03/04

Vom Programm zur Machineninstruktion • a, b und c sind Datenfelder für ganze Zahlen. • Die Instruktionen beziehen sich über Adressen auf diese Felder. Einfache Transport-instruktionen Bedeutung: mov nach, von add: ein Operand muss in einem Register stehen. Ergebnis im Register. Einf. in die WI 1 - DV-Infrastruktur WS03/04

Vom Programm zur Machineninstruktion • if (c>=0) c=-3*c; • else c=2*c; Einf. in die WI 1 - DV-Infrastruktur WS03/04

IO-Instruktionen • Neben der mov-Instruktion, die für den Datenaustausch zw. Registern und Speicher zuständig ist, gibt es die Instruktionen • in reg,ioport und • out ioport,reg , • die Daten zwischen den Registern und den Steuereinheiten von IO-Geräten bewegen (z.B. Tastatur, Bildschirm, Festplatte). Einf. in die WI 1 - DV-Infrastruktur WS03/04

Die Register und ihre Verwendung Register müssen bei der Assemblerprogrammierung berücksichtigt werden. Einf. in die WI 1 - DV-Infrastruktur WS03/04

Fortsetzung der Registeraufzählung Einf. in die WI 1 - DV-Infrastruktur WS03/04

Einschub: Hexadezimal • Mit den Dualzahlen kann man wegen der vielen Stellen schlecht umgehen. Daher werden Dualzahlen meist als Hexadezimal-zahlen dargestellt, das sind Zahlen zur Basis 16. Die Ziffern dieser Zahlen sind • 0,1,2,3,4,5,6,7,8,9,A,B,C,D. • Die Hexadezimalzahl 3C5A • ist 3*163+12*162+5*161+10*160=15450 Einf. in die WI 1 - DV-Infrastruktur WS03/04

Einschub: Hexadezimal • Dual <--> Hexadezimal • Man bildet bei dual von rechts 4er Päckchen. Der Dualwert wird als Hexaziffer dargestellt. • 0110 1111 1010 0011 dual • 6 F A 3 hexa Einf. in die WI 1 - DV-Infrastruktur WS03/04

Maschinensprache, gesehen im Debug-Modus Microsoft Visual Studio C++ mov a,2 mov b,8 mov eax,a add eax,b mov c,eax Einf. in die WI 1 - DV-Infrastruktur WS03/04

..noch Maschinensprache Einf. in die WI 1 - DV-Infrastruktur WS03/04

c = a+b; mov eax,a add eax,b mov c,eax Daten a c b Einf. in die WI 1 - DV-Infrastruktur WS03/04

Zahlenspielereien Zur Erinnerung: Zahl der Werte N<= 2n n = Zahl der Bitstellen Einf. in die WI 1 - DV-Infrastruktur WS03/04

Codierung der Daten Ganze Zahlen ohne Vorzeichen • am Beispiel 8 Bit • Dualdarstellung mit den Wertigkeiten • 27 26 25 24 23 22 21 20 • Beispiel: • 0 1 1 0 1 1 0 0 • 0*128+1*64+1*32+0*16+1*8+1*4+0*2+0*1 = 108 Einf. in die WI 1 - DV-Infrastruktur WS03/04

Ganze Zahlen • Zahlenstrahl • 00000000 00000001 00000010 ............... 11111111 • Was passiert, wenn auf die größte Zahl 11111111 eine 1 addiert wird? • Die neue Zahl ist mit 8 bit nicht mehr darstellbar: 1 00000000 • In der Rechnertechnologie gibt es diese neunte Stelle nicht, das Ergebnis ist 00000000, d.h. die kleinste Zahl. • Daher gibt es keinen Zahlenstrahl, sondern eine ringförmige Anordnung. • Übrigens wird die abgeschnittene 1 als Überlauf zur weiteren Verwendung anderswo abgespeichert. (Carry-Bit oder -Flag) Einf. in die WI 1 - DV-Infrastruktur WS03/04

Codierung der Daten A Wird der Punkt A durchlaufen, wird Carry gesetzt, das Ergebnis ist mathematisch falsch. B Einf. in die WI 1 - DV-Infrastruktur WS03/04

Umwandlung Dezimal-Dual Einf. in die WI 1 - DV-Infrastruktur WS03/04

Codierung der Daten Wird der Punkt B durch-laufen, wird die Vorzei-chenstelle überschrieben: Overflow wird gesetzt, das Ergebnis ist mathe-matisch falsch. Bei diesen (negativen) Werten ist das Bit ganz links gleich 1. Einf. in die WI 1 - DV-Infrastruktur WS03/04

Codierung der Zeichen • Was sind Zeichen? • Buchstaben • Ziffern • Sonderzeichen Einf. in die WI 1 - DV-Infrastruktur WS03/04

Codierung der Zeichen Einf. in die WI 1 - DV-Infrastruktur WS03/04

Gleitkommazahlen (reelle Zahlen) • Die Gleitkommaarithmetik wird in einem extra Prozessor (Bezeichnung Coprozessor) ausgeführt, der früher separat war, heute jedoch im Prozessor integriert ist. • Trifft die CPU auf eine Gleitkomminstrution, so aktiviert sie den Coprozessor. Dieser führt die Instruktion parallel aus. Einf. in die WI 1 - DV-Infrastruktur WS03/04

Gleitkommazahlen (reelle Zahlen) Einf. in die WI 1 - DV-Infrastruktur WS03/04

Gleitkommazahlen (reelle Zahlen) Einf. in die WI 1 - DV-Infrastruktur WS03/04

Gleitkommazahlen (reelle Zahlen) • Normalisierte Darstellung üblich. • Typ double z.B. • +/- 1.001110100001...100 * 211100011001 • Vorzeichen • 52 Bit Mantisse 11 Bit Exponent Einf. in die WI 1 - DV-Infrastruktur WS03/04

Gleitkommazahlen (reelle Zahlen) Einf. in die WI 1 - DV-Infrastruktur WS03/04

Gleitkommazahlen (reelle Zahlen) 0xZahl : Hexazahl! Einf. in die WI 1 - DV-Infrastruktur WS03/04

CPU Technik • Eine CPU arbeitet getaktet. CPU Taktgeber, Quarz Einf. in die WI 1 - DV-Infrastruktur WS03/04

CPU Technik • Taktfrequenz im ersten PC • CPU 8088: 4,5 MHz • heutige Taktfrequenzen • Pentium III zwischen 500 und 1400 MHz • Pentium 4 zwischen 1,5 GHz und 3,2 GHz • Celeron zwischen 1,2 GHz und 2,7 GHz • Athlon zwischen 1,4 GHz und 3,2 GHz Einf. in die WI 1 - DV-Infrastruktur WS03/04

CPU Technik • Klassen von CPU‘s • CISC Complex Instruction Set Computer --Die CPU hat viele und komplexe Instruktionen. (Intel, AMD) • RISC Reduced Instruction Set Computer -- Die CPU hat wenige einfache Instruktionen. (Apple, IBM: PowerPC; SUN) • Unterschied: Die Machinenprogramme bei RISC sind länger, da komplexe Instruktionen durch die einfachen Instruktionen nachgebildet werden müssen. Vorteil von RISC: Ausführung der Instruktionen einfacher und schneller. Einf. in die WI 1 - DV-Infrastruktur WS03/04

CPU Technik CPU L1 L2 BUS-Systeme IO Speicher Einf. in die WI 1 - DV-Infrastruktur WS03/04

CPU Technik • BUS: Verbindung zwischen Bausteinen Der Front Side Bus ist die Ver-bindung der CPU zu den BUS-Systemen, seine Geschwindig-keit ist eine Kenngröße der CPU, gemessen in MHz (max. Taktfrequenz des Bus). Die MHz-Angabe muss aber nicht die tatsächliche Daten-rate festlegen. Einf. in die WI 1 - DV-Infrastruktur WS03/04

Celeron 1700 Taktfrequenz (MHz): 1700Bauart: Sockel 478CPU-Kern: WILLAMETTEFSB in (MHz): 400Level 1 Cache: 8kBLevel 2 Cache: 128kBBefehlssätze: MMX, SSE2, Advanced Transfer Cache (ATC), Hyper Pipelined, NetBurst, Rapid Execution EngineCore Spannung: 1.75V Preis ca. 70€ Realisierungsversion Versorgungsspannung Einf. in die WI 1 - DV-Infrastruktur WS03/04

Pentium 4 3000 • Taktfrequenz (MHz): 3000Bauart: Sockel 478CPU-Kern: NORTHWOODFSB in (MHz): 800Level 1 Cache: 8kBLevel 2 Cache: 512kBBefehlssätze: MMX, SSE2, Advanced Transfer Cache (ATC), Hyper Pipelined, NetBurst, Rapid Execution Engine HyperthreadingCore Spannung: 1.5V • Preis ca. 430€ Einf. in die WI 1 - DV-Infrastruktur WS03/04

Athlon XP 3200+ • Taktfrequenz (MHz): 2200Bauart: Sockel ACPU-Kern: BARTONFSB in (MHz): 400Level 1 Cache: 128kBLevel 2 Cache: 512kBBefehlssätze: MMX, ISSE, 3D Now! ProfessionalCore Spannung: 1.65V • Preis ca. 360€ Einf. in die WI 1 - DV-Infrastruktur WS03/04