Overview of Basic LC-3 Instructions: Operate, Data Movement, and Control Branching

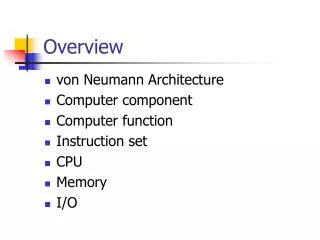

This document provides a comprehensive overview of the LC-3 instruction set, detailing the fundamental operate, data movement, and control instructions. It explains the ADD, AND, and NOT operations alongside data movement commands like LOAD and STORE. Detailed examples illustrate branching instructions (BR, JMP, TRAP), emphasizing their functions and how to execute them correctly. Additionally, a sample program for computing the sum of integers and a multiplication example are included, demonstrating effective usage of these instructions in practical applications.

Overview of Basic LC-3 Instructions: Operate, Data Movement, and Control Branching

E N D

Presentation Transcript

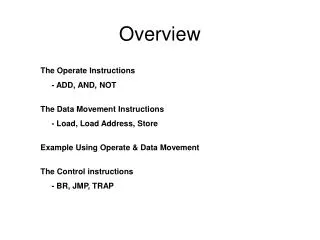

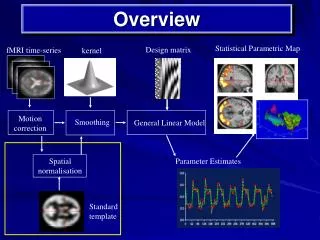

Overview The Operate Instructions - ADD, AND, NOT The Data Movement Instructions - Load, Load Address, Store Example Using Operate & Data Movement The Control instructions - BR, JMP, TRAP

Example Opcode

Branch Instruction BR [0000 nzp PCoffset9] • Branch specifies one or more condition codes • If the set bit is specified, the branch is taken: • PC is set to the address specified in the instruction • Target address is made by adding SEXT(IR[8:0]) to the PC • If the branch is not taken: - the next sequential instruction (PC) is executed.

BR ///////////// ///// + SEXT

Jump Instruction JMP BaseR [1100 000 BaseR 000000] • Jump is an unconditional branch -- always taken. • Base • Address is contents of the register • Allows any target address.

TRAP • Calls a service routine, identified by 8-bit “trap vector.” • When routine is done, PC is set to the instruction following TRAP.

Using Branch Instructions • Compute sum of 12 integers.Numbers start at location x3100. Program starts at location x3000. R1 x3100R3 0R2 12 R2=0? R4 M[R1]R3 R3+R4R1 R1+1 R2 R2-1 NO YES

clear R2 add R4 to R2 decrement R5 R5 = 0? No Yes HALT Example 1: Multiply • This program multiplies two unsigned integers in R4 and R5. x3200 0101010010100000 x3201 0001010010000100 x3202 0001101101111111 x3203 0000011111111101 x3204 1111000000100101 R2 <- 0 R2 <- R2 + R4 R5 <- R5 – 1 BRzp x3201 HALT