DSP Digital Signal Processors

270 likes | 478 Views

DSP Digital Signal Processors. Entorno de desarrollo con Sharc. Indice. Introducción a los DSP Arquitectura ADSP-2106x Sharc Entorno de desarrollo Talk-throu, FIR y Squelch. Introducción a los DSP. DSP=P especializado para señal en tiempo real Convolución, Fourier, Correlación:

DSP Digital Signal Processors

E N D

Presentation Transcript

DSP Digital Signal Processors Entorno de desarrollo con Sharc Introducción a los DSP

Indice • Introducción a los DSP • Arquitectura ADSP-2106x Sharc • Entorno de desarrollo • Talk-throu, FIR y Squelch

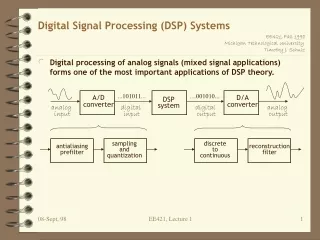

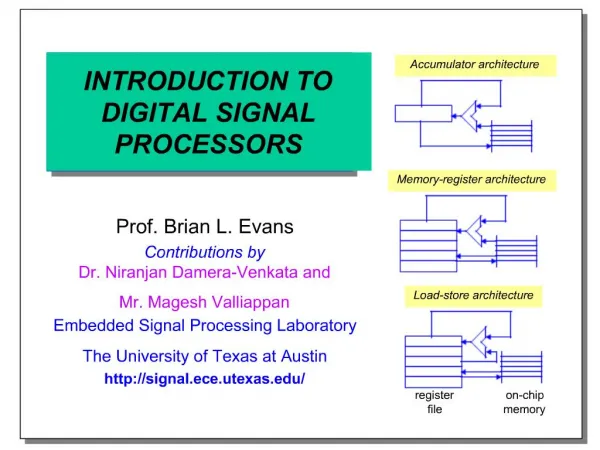

Introducción a los DSP • DSP=P especializado para señal en tiempo real • Convolución, Fourier, Correlación: xi yj • Multiplicar y ACumular. Operación MAC • 2 memorias, 2 buses de datos

Introducción a los DSP • Control de Saturación • Overflow “analógico” vs. complemento a 2 • Pipelining • Leer instrucción, operandos, operar, escribir

x3 … x2 x1 x0 xN-1 xN-2 … Introducción a los DSP • Datos y programa separados • Arquitectura Harvard • Buffer circular • Gestión automática • Inversión de bits de direcciones para FFT

Historia • NEC µPD7720 and AT&T DSP1. año 1980 • Texas Instruments TMS32010, … 1983 • Los más extendidos • Motorola 56000 • Analog Devices 2101, … • Fácil programar • Improv Systems Jazz DSP. 1999 • configurable VLIW • Ceva GNU Free Documentation Licensehttp://en.wikipedia.org/wiki/Digital_signal_processor

Amplia gama • ADSP-21xx • Amplia y variada familia compatible entre sí • SHARC • Super Harvard • Coma flotante • TigerSHARC • Más potente • Blackfin • Ajustados consumo y prestaciones para dispositivos móviles

Arquitectura Sharc. Cómputo • Unidades independientes • MAC, ALU, Shifter • En un ciclo se puede: • Leer 4 operandos • Escribir 2 resultados

Arquitectura Sharc. Cómputo • Formatos numéricos • Coma fija 32 bits • Coma flotante 32 ó 40 bits • Para coma fija • Acumulador extendido de 80 bits • Para evitar overflow y underflow 0’40’2 = 0’08 0’0 + 0’3 0’5 = 0’15 0’1 = 0’23 0’2 0’1

Arquitectura Sharc. DAG, Generador de Direcciones • Bit reversing para la FFT

Arquitectura Sharc. DAG, Generador de Direcciones • Pre/post modify • + flexible que 21xx • Bufferes circulares en cualquier posición

Arquitectura Sharc. Secuenciador de Programa • Cache de instrucciones • 3 buses efectivos: x, y, instrucciones • Predice saltos • Pipeline: fetch, decode, execute

Arquitectura Sharc. Secuenciador de Programa • Instrucciones de 48 bits. Ortogonal • Casi decodificadas • Bucle sin consumir ciclos • Interrupciones sin consumir ciclos • Juegos secundarios de registros generales • PC stack, Loop stack • Cada muestra una interrupción

Arquitectura Sharc. Memoria • 32 bits de direcciones • Interna, otros procesadores, externa • Memoria interna total: • 21061 – 1 Mbit • 21060 – 4 Mbit • 21062 – 2 Mbit • Dividida en 2 bancos configurables • DM (32 bit) + PM (48 bit) • EZ-KIT 21061 Sharc: • Banco 0 = 8 kW PM + 4 kW DM(Y) • Banco 1 = 16 kW DM(X) 8kWp 48bit/Wp + (4 +16)kWd 32bit/Wd = 384+640 = 1024 kbit

SHARC EZ-KIT LITE Document Library • Getting Started with the SHARC EZ-KIT LITE • SHARC EZ-KIT LITE Reference Manual • ADSP-21000 Family Development Software Tools Release Note • ADSP-21000 Family Assembler Tools • ADSP-21000 Family C Tools Manual • ADSP-21000 Family C Runtime Library Manual • ADSP-2106x SHARC User’s Manual • ADSP-2106x Family Data Sheets • Digital Signal Applications Using the ADSP-21000 Family, Vol.1 • SHARC Third Party Information

Tarjeta de desarrollo SHARC EZ-KIT LITE • ADSP 21061 • Codec AD/DA • Audio In/Out • LEDs, 5 • Botones, 3

Software de desarrollo. Analog • Programa EZ-KIT LITE Host, para: • Cargar, ejecutar programas • Ver memoria • Probar demos • Visual DSP++ • Entorno integrado • Línea de comandos • Compilar, cargar, depurar. • VisualAudio, VisualFone,… • Bloques, librerías,…

Software de desarrollo. TDSII, ezplot • Editar programa en C (pág. 2.1) • ezkit.h facilita acceso al hardware (pág. 2.3) • Abrir sesión DOS, icono EZKit Sharc 21k Tds • Compilar: Makeprograma • Cargar: Loadprograma • Monitorizar con ezplot • Conectar y medir in/out estéro • hmake y hload permiten usar consola PC

Monitorizar con Ezplot • Permite ver la memoria del DSP • Númerica y gráficamente • Valores y vectores • En tiempo y en frecuencia • Se configura en ezplot.cfg • Ayuda de opciones en ezplot.txt (pág. 2.7)

xi[n] n 0 1 2 3 4 5 xo[0] xo[1] xo[2] xo[3] xo[4] xo[5] Procesado de muestra, codec_inout Procesado de trama, main Talk-throu • Inicializar • En cada interrupción de muestra: • Left input (Procesado nulo) Left output • En main: • Espera

x3 x3 … … x2 x2 x1 x1 x0 x0 xN-1 xN-1 xN-2 xN-2 … … r=0.9 =/4 r |H()| f fs/2 Filtro FIR • En prelab calcular: • Coeficientes y • Respuesta frecuencial • Escribir programa • Función de librería, Buffer, … • En laboratorio • Implementar FIR • Comprobar respuesta

![Global Digital Signal Processors [DSP] Market Forecast](https://cdn4.slideserve.com/1477223/marketsandmarkets-presents-dt.jpg)