CCT FPGA CNES - ALCATEL

130 likes | 301 Views

Centre de Compétence Technique CNES FPGA ALCATEL Space Département TTN BO/CR/NA 30/11/2001 Sandrine Auguié / Jean-Marie Garigue. CCT FPGA CNES - ALCATEL. Utilisations des FPGAs à ALCATEL Space (1/3) Deux champs d’application Embarqué Prototypage rapide d’ASICs complexe Embarqué Applications

CCT FPGA CNES - ALCATEL

E N D

Presentation Transcript

Centre de Compétence Technique CNESFPGAALCATEL SpaceDépartement TTNBO/CR/NA30/11/2001Sandrine Auguié / Jean-Marie Garigue

CCT FPGA CNES - ALCATEL • Utilisations des FPGAs à ALCATEL Space (1/3) • Deux champs d’application • Embarqué • Prototypage rapide d’ASICs complexe • Embarqué • Applications • traitement de données (gestion mémoire, multiplexage) • télécom (modulation et codage) • carte processeur (glue logique, co-processeur) • FPGAs de type anti-fusible (ACTEL) • A1020, A1280, RH1020, RH1280, A54SX16/32 • Expérience • 10 ans d’utilisation • plus de 50 designs modèles de vol déjà réalisés

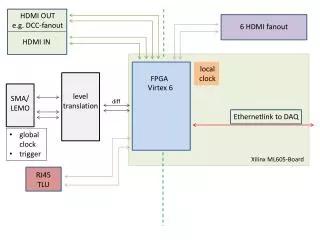

CCT FPGA CNES - ALCATEL • Utilisations des FPGAs à ALCATEL Space (2/3) • Maquettage des ASICs complexes • Utilisation de FPGAs SRAM (XILINX) • Vérification dans l’équipement avec utilisation d’une plaquette d’adaptation ASIC->FPGA • Utilisation de Virtex-E 800 à 2000 en BGA560 • Mise en oeuvre de grande quantité de mémoire intégrée • Développement de «proof of concept» • Validation algorithme de traitement hors équipement • Bancs de test FPGAs intégrant jusqu’à 6 cartes avec 4 Virtex 1000, possibilité d’intégrer des cartes ADC, DAC (Validation processeur numérique transparent, turbo-décodeur, …) • Mise en oeuvre LVDS • Complémentaires des solutions émulation hardware également utilisées : aspects analogiques et «at speed»

CCT FPGA CNES - ALCATEL • Utilisations des FPGAs à ALCATEL Space (3/3) • Conclusion • 2 sources privilégiées • ACTEL (RH1020, RT54SX16/32) • XILINX (Virtex, Virtex-e) • 2 champs d’application • Embarqué : 50 designs en ACTEL • Prototypage : bancs de test et “proof of concept” en XILINX

CCT FPGA CNES - ALCATEL • Moyens • Machines : • Work Stations • Sunblades+U80 • Logiciels • Renoir • SPW • Modelsim • Leonardo • FPGA Compiler • Velocity • FormalPro

CCT FPGA CNES - ALCATEL • Retour d’expérience : technologies (1/3) • Antifusible (ACTEL) • Alertes composant • incertitudes à la mise sous tension, séquencement d’alimentation, polarisation de certaines broches • Alertes causées par la complexité et la nouveauté du produit, beaucoup plus fréquentes sur la RT54SX que sur les familles précédentes (peu de délai entre la version civile et la version RT) • Défaillance en programmation • Documentation et information technique : • Produit U.S. => difficulté d’obtenir des informations techniques rapidement sur certains cas de mise en œuvre • Obsolescences • Brutale sur la RT54SX (le produit était à peine qualifié) • Mise en évidence des limites du schéma “fabless” • Fiabilité, tenue aux SEUs, bon support

CCT FPGA CNES - ALCATEL • Retour d’expérience : technologies (2/3) • SRAM (XILINX) • Difficultés pour approvisionner les nouvelles séries en petite quantité et dans des délais courts • Produits très complexes • Standard d’IO en grand nombre, mémoire enfouie • Sensibilité de la performance en layout au placement des entrées/sorties • Grosses matrices disponibles uniquement en BGA • Evolution très rapide des tension d’alim avec les nouvelles familles • => Difficulté de mise en œuvre des produits • Produits jamais mis en œuvre en embarqué • un grand nombre de difficultés de mise en œuvre reste sans doute à voir. • Produits performants, outils XILINX puissants

CCT FPGA CNES - ALCATEL • Retour d’expérience : technologies (3/3) • Conclusion • Difficultés liées à l’évolution rapide des technologies et à leur perennité plus réduite • Pas de difficultés majeures au niveau design • Difficultés de mise en œuvre

CCT FPGA CNES - ALCATEL • Retour d’expérience : outils (1/2) • Antifusibles et SRAM : • Marché FPGA de plus en plus orienté vers le développement sur PC, inquiétude pour l’avenir de la part des utilisateurs de station de travail • Evolution permamente des versions d’outils, extrèmement difficile d’avoir une configuration stable. • Pas de leadership sur la synthèse, difficulté de trouver le “bon” outil, outils très buggés • Impossibilité de travailler avec un analyseur de timing standard, obligation de travailler avec ceux des fournisseurs (souvent moins performants) • Antifusibles : • Marché de niche, donc peu d’intérêt des fournisseurs de CAD, donc difficulté pour avoir les bibliothèques pour tous les outils. • Résolutions des bugs tardive

CCT FPGA CNES - ALCATEL • Retour d’expérience : outils (2/2) • Conclusion • Evolution très rapide des versions d’outils, beaucoup de bugs • Difficultés pour avoir les bibliothèques spécifiques à certains outils (preuve formelle, analyse statique de timing)

CCT FPGA CNES - ALCATEL • Orientation ALCATEL pour les futurs projets • Prototypage • Poursuite avec XILINX en capitalisant sur l’expérience acquise, évolution vers VIRTEX 2. • FPGAs Embarqués • Capitalisation de l’acquis et de la confiance avec ACTEL, embarquement des nouvelles familles RT54SX-S. Gros intérêt pour la 72S • Recherche d’une alternative à ACTEL, avec des fondeurs spaciaux • ATMEL • UTMC • Recherche de la performance, de la flexibilité, et d’un écart réduit avec le commercial avec XILINX (Virtex, Virtex-e, …)

CCT FPGA CNES - ALCATEL • Attentes ALCATEL pour le futur • Fin de la situation de monopole ACTEL • Augmentation de la capacité (vers 1M de portes ?) • Intégration de mémoires enfouies • Intégration d’interfaces rapides : LVDS • Diminution des contraintes de mise en œuvre : • Stabilité à la mise sous tension • Séquence d’alimentation simplifiées • Disponibilité d’alternatives aux boîtiers BGA • Amélioration de la chaîne de développement

CCT FPGA CNES - ALCATEL • Conclusion • Qualification de la famille RT54SX-S • Qualification des XILINX VIRTEX et développement d’une méthodologie de durcissement aux SEUs • Développements ATMEL