Computer Architechture

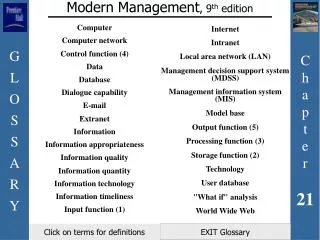

Computer Architechture. Team DataPath Research. PC and IF in the Processor. Program Counter & Instruction Fetch. PC Instruction address register Increments after fetch to read next instruction Jumps, branches, subroutines, & returns Instruction Fetch

Computer Architechture

E N D

Presentation Transcript

Computer Architechture Team DataPath Research

Program Counter &Instruction Fetch • PC • Instruction address register • Increments after fetch to read next instruction • Jumps, branches, subroutines, & returns • Instruction Fetch • Copies the address in the PC into the IR • Retrieves the instruction content from memory

PC & IF Inputs and Outputs • Inputs • Instruction Memory • Incrementor • Control Line • Outputs • Databus to Instruction Decode

Instruction Types • R-Type (Register Only) • I-Type (Immediate Value) • J-Type (Jump)

The Register File! • What is it? • Contains all 32 registers; some available to the programmer • Registers are designated using 5 of the bits in the instruction • Each register contains 32 bits of information • What does it do? • Controls the flow of information to or from registers • Reads two registers at a time and writes to one • Receives a control bit for knowing when to write • Reads from registers on the positive edge of the clock cycle and writes to a register on the negative edge

The Register File! Lets learn how to read! From Computer Organization & Design: The Hardware/Software Interface • The 5 bits determining the registers are used to control a Mux that picks from 32 registers. (5 bits = 32 distinct bit sequences) • Data is passed along to the ALU. • This all happens when either the "Write" (from Figure B.8.8) is on or off and during the rising edge of the clock cycle.

The Register File! How about writing? From Computer Organization & Design: The Hardware/Software Interface • Register number is determined in the decoder which, when ANDed with "Write", sets that register to have it's data overwritten. • The data being written is coming from the ALU on a 32 bit bus connected to each register. • Performs the write to the register when the clock cycle has a negative slope.

The Register File!Going a little deeper... Implementation: Registers • Each bit of a register can be made up of D-Flip Flop • The D signifies the data that is being inputted. • Q is the output, where the bit is read from Writing • Uses 32:1 Mux for toggling the appropriate register • ANDs this signal with the RegWrite control signal to enable writing to register • A 32 bit bus is attached to each register Reading • A 32x32 to 32 Mux must be used. This type of Mux chooses between 32 registers with 32 bits each and outputs the 32 bits of the chosen register designated in 5 bits in the instruction • One method of implementing this is to use 32, 32 to 1 Multiplexers D-Flip Flop From physicsforums.com

The ALU and You! Fig 4.2 Computer Organize and Design

Fun Facts • What is an alu? • Main brain Mclain of the PLP Architecture • Combination of Adders and Logic Gates • What does it do? • Performs Mathmatical and Logical Operations • Why do we need it? • Allows us to process Data in a multitude of ways

3 ALUs within PLP Architecture. • PC incrementation • Branching Instructions • R and I-type Arithmetic and Logical Instructions

ALU R-type Instruction Example From PLP wiki

Simple Data Path Branching R-type I-type Fig. 4.11 Computer Organize and Design

Oh It makes sense • Function determined by Control • ALU gives us POWAH • Can do process data in a multitude of ways

Mux, Sign Extension, Logical Shift, and Branching and Jumping • Mux (Multiplexer) • It is used anytime you need to make a decision between multiple inputs • Sign Extension • It is used to keep a number value the same but have the number take up more bits • Logical Shift • It is used to move the information in a word to right or left • Branching and Jumping • They are used to move from one line of code to another

Inputs and OutputsMux, Sign Extend and Logical Shift • Mux • 3 inputs and 1 output • Sign Extend • In this example there are 16 inputs and 32 outputs • Logical Shift • In this example there are 8 inputs and outputs • The number of outputs will always equal the number or inputs

Where They Fit InMux, Sign Extension, and Logical Shift • Mux, Sign Extend and Logical Shift • These are all used many times in the mips architecture and they can be used or placed anywhere one of these operations is needed

Branching and Jumping • Branching (Orange) and Jumping (Blue) • They take many inputs form many different parts of the architecture and it outputs back to the program counter

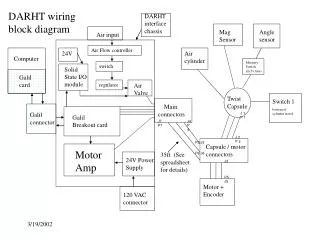

Blue lines: control signals (MemWrite, MemRead) Black lines: 32-bit values (Address, Write data, Read data) The Memory: Structure It is a 232x32 memory

If the data memory is to be read => • MemRead=1 (the active signal) • MemWrite=0 • If the data memory is to be written => • MemRead=0 • MemWrite=1 (the active signal) • Address? • Write data? • Read data?

The instructions • R-type instruction, add, sub, and, or, slt... • MemWrite and MemRead are set to 0, • Memory doesn’t have to do anything. • Branch instructions, • MemWrite and MemRead are set to 0, • Memory doesn’t have to do anything. • Lw instruction, • MemWrite is set to 0 and MemRead to 1. • Need to compute the effective address =>sign extend. • ALUOp should be ADD (010). • ALUSrc fixed to 1. Complete address in its line => value wanted at Read data • Sw instruction, • MemRead is set to 0 and MemWrite to 1. • Need to compute the effective address => sign extend. • ALUOp should be ADD (010). • ALUSrc fixed to 1. We put the data in the Write data => value saved at the specified address

Two New Instructions • Variable Logical Shift Left (sllv) • Purpose: shift left by a number of bits that is unknown to the programmer. The shift is stored in a register instead of in an immediate value. • Variable Logical Shift Right (srlv) • Purpose: shift right by a number of bits that is unknown to the programmer. The shift is stored in a register instead of in an immediate value.

Two New Instructions Cont. • Current implementation example: li $t0 5 loop: slli $t1, $t2, 0x1 subi $t0, $t0, 1 // value shift counter bne $t0,$Zero,loop • Example with new instructions sllv $t1, $t2, $t0 • This saves 3n-2 instructions.

Wrap-Up • Research will enable code implementation of a PLP-architecture processor. • The hardware will comprise all five stages of the processor. • Behavioral Verilog code will "construct" the processor within an FPGA. • Questions?